# A HIGH POWER WIDE BANDWIDTH SWITCHMODE AMPLIFIER

FRANK M. FLINDERS

ASTER OF ELECTRICAL ENGINEERING

## A HIGH POWER WIDE BANDWIDTH SWITCH MODE AMPLIFIER

### FRANK M. FLINDERS B.Eng

Dissertation submitted in partial fulfillment of the requirements for the degree of Master of Engineering

University of Central Queensland James Goldston Faculty of Engineering Department of Electrical Engineering

1 March 1993

1840495.

T1001106821

COMPUTER LOAN

Form RHD 48

F557 2

#### CONFIRMATION OF DEPOSITION

(to be appended to thesis on submission of hard bound copy to the University Library)

PART A (Candidate to complete. Please print in black ink)

| Candidate's N | lame: | Free    | Kthed   | wei e    | Degree: h    | vicz., t. i | $\cdot, \cdot, \cdot$ |

|---------------|-------|---------|---------|----------|--------------|-------------|----------------------------------------------------------------------------------------------------|

| Thesis Title: | Ň     | ic' H   | Person. | tse este | Para Wiellie | xx. A. F.   | : • • <b>,</b> • X •                                                                               |

|               | (-)p  | States. |         |          |              |             |                                                                                                    |

PART B (Office Use Only)

As at the date recorded below and in keeping with the Requirements for the Submission Presentation and Deposition of Research Theses, the thesis described above has been deposited in the University Library.

#### Signature Redacted

SIGNATURE (SPECIAL COLLECTIONS LIBRARIAN)

57 · 10 · 23 (date)

(The signed Confirmation of Deposition must be forwarded directly to the Research Services Office)

CURAMSARIAS

#### A HIGH POWER WIDE BANDWIDTH SWITCH MODE AMPLIFIER.

**ABSTRACT:** This thesis describes the development of a 45kVA, 20kHz bandwidth switching amplifier. The amplifier is a subsection of a controlled source audiomagnetelluric (AMT) system primarily aimed at exploration of mineral deposits and geophysical deposits associated with oil and gas fields. However this amplifier has applications in many other areas.

A number of design innovations contributing to the body of knowledge in power electronics were implemented in the course of the development of the AMT amplifier. In particular, a new bridge inverter topology has been developed which supports five level pulsewidth modulation with only four switches. In the past eight switches have been required to achieve the same result. The five level modulation has allowed extension of the bandwidth and improvement in the output quality of the amplifier without increase in the switch frequency.

The new bridge topology consists of four buck converter sub units coupled by transformers. The buck converters supply a maximum current of 100A from a 560V nominal bus and switch at 50kHz. Each buck converter employs an Insulated Gate Bipolar Transistor and high speed power diodes together with a regenerative snubbing and clamp system to achieve this high power frequency product. New techniques have been developed to accurately predict diode reverse recovery performance during of the buck converter design process.

The new converter topology requires a specialised control system. The design of this control system, as well as important design rules developed during the project, are presented.

Computer simulation studies have been extensively used in the design of both the buck converters and the control system. This design approach has resulted in a significant reduction in time consuming prototype modifications.

## TABLE OF CONTENTS

| ABSTRACT                                           | i   |

|----------------------------------------------------|-----|

| FIGURE LIST                                        | vi  |

| ACKNOWLEDGEMENTS                                   | x   |

| DECLARATION                                        | xi  |

| PUBLICATIONS                                       | xii |

| 1. INTRODUCTION                                    | 1   |

| 2. CONVERTER TOPOLOGY                              | 11  |

| 2.1 Conventional Converter Topologies              | 11  |

| 2.2 Multilevel Modulation                          | 16  |

| 2.3 The New Five Level Converter Topology          | 28  |

| 2.4 Coupling Transformer Selection                 | 31  |

| 2.5 Buck Converter Cell Topology                   | 35  |

| 3. POWER DEVICE MODELING                           | 43  |

| 3.1 Power Diode Physics                            | 43  |

| 3.2 Power Diode Turn Off Characteristics           | 50  |

| 3.3 Power Diode Turn On Characteristics            | 77  |

| 3.4 Power Diode Forward Conduction Characteristics | 84  |

| 3.5 IGBT Characteristics                           | 85  |

| 3.6 IGBT Conduction Power Loss                     | 87  |

| 3.7 IGBT Switching Power Loss                      | 88  |

|                                                    |     |

### 4. POWER CIRCUIT DESIGN

4.1 General Considerations 97

| 4.2 Selection of the Snubber Capacitor and   |     |

|----------------------------------------------|-----|

| Commutating Inductor                         | 98  |

| 4.3 Snubber Module Design                    | 120 |

| 4.4 Clamping System Design                   | 135 |

| 4.5 Freewheel Diode Module Design            | 142 |

| 4.6 IGBT Module Design                       | 155 |

| 4.7 Determination of the Cooling Requirement | 164 |

| 4.8 Buck Converter Experimental Results      | 170 |

| 5. CONTROLLER OPERATION AND DESIGN           |     |

| 5.1 Control Strategy                         | 177 |

| 5.2 Phase/Ramp Generator Operation           | 184 |

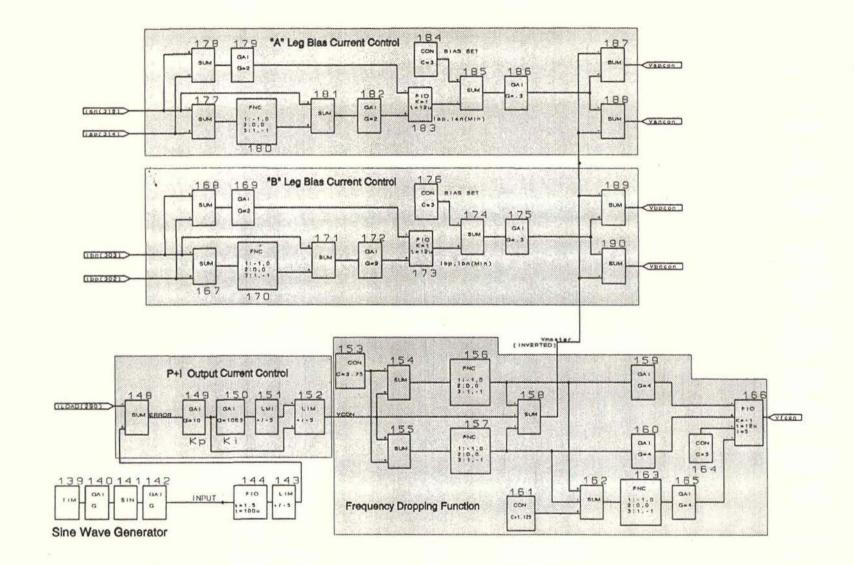

| 5.3 Bias Current Control Operation           | 194 |

| 5.4 Output Current Control Operation         | 196 |

| 5.5 Current Limiter Operation                | 202 |

| 5.6 Control Systems Design                   | 204 |

| 6. SIMULATION AND SCALE MODEL TEST RESULTS   | 227 |

| 6.1 Simulation Technique                     | 227 |

| 6.2 Small Scale Model and Simulation Results | 230 |

| 7. CONCLUSIONS                               | 241 |

| 8. REFERENCES                                | 244 |

| APPENDIX A. SOI SPICE MODEL                  | 250 |

| APPENDIX B. SELECTION OF RESISTOR Rf         | 253 |

| APPENDIX C. DIODE D <sub>f</sub> REVERSE RECOVERY CALCULATION | 256 |

|---------------------------------------------------------------|-----|

| APPENDIX D. DRIVE CARD SCHEMATIC DIAGRAM                      | 258 |

| APPENDIX E. SPICE MODEL OF DRIVE CARD                         | 259 |

| APPENDIX F. DIODE D <sub>c</sub> REVERSE RECOVERY CALCULATION | 262 |

| APPENDIX G. AMPLIFIER PHOTOGRAPHS                             | 263 |

# FIGURE LIST

|             |                                                                                                 | Page |

|-------------|-------------------------------------------------------------------------------------------------|------|

| Figure 2.1  | Cuk Converter Operation                                                                         | 13   |

| Figure 2.2  | Bridge Inverter Modulation Techniques                                                           | 15   |

| Figure 2.3  | Conventional Five Level Topologies                                                              | 17   |

| Figure 2.4  | Five Level Modulation Waveform                                                                  | 18   |

| Figure 2.5  | Two, Three and Five Level Switching<br>Strategy Comparison                                      | 19   |

| Figure 2.6  | Current Ripple Improvement of 5 Level Over<br>2 Level Modulation as a Function of Duty<br>Ratio | 21   |

| Figure 2.7  | Current Ripple Improvement of 5 Level Over<br>3 Level Modulation as a Function of Duty<br>Ratio | 22   |

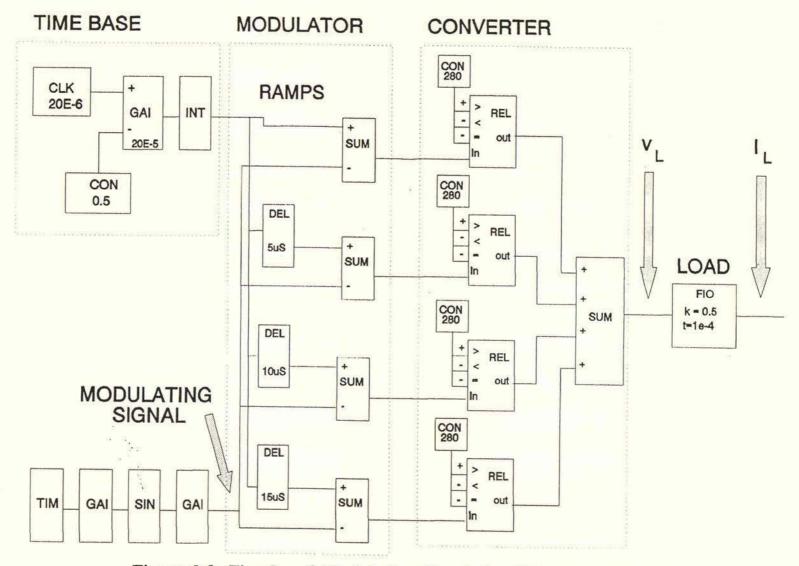

| Figure 2.8  | Five Level Modulation Simulation "TUTSIM"<br>Model                                              | 24   |

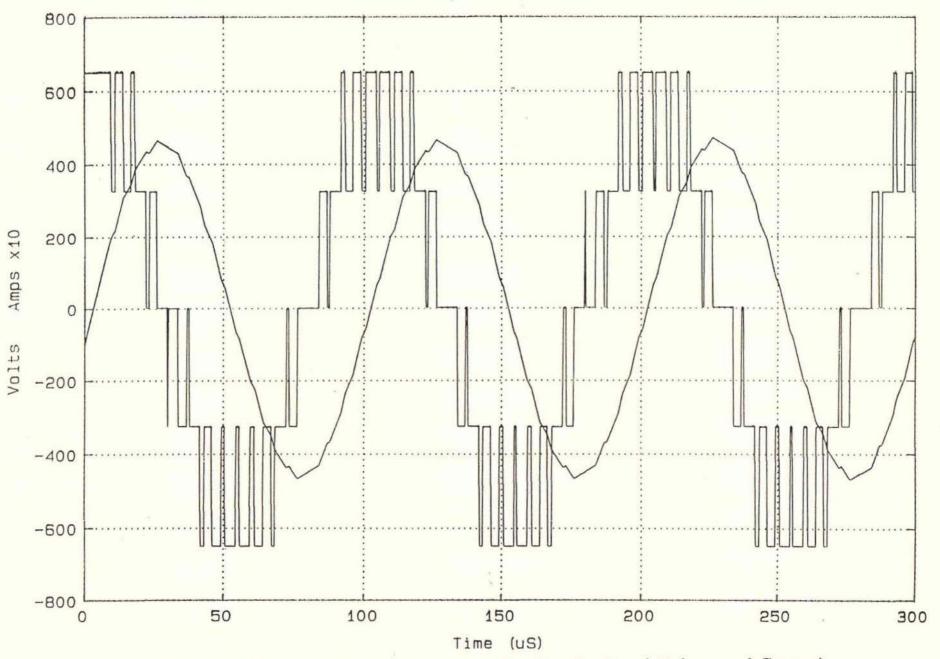

| Figure 2.9  | Five Level Modulation Simulation Results<br>(Load Voltage and Current)                          | 25   |

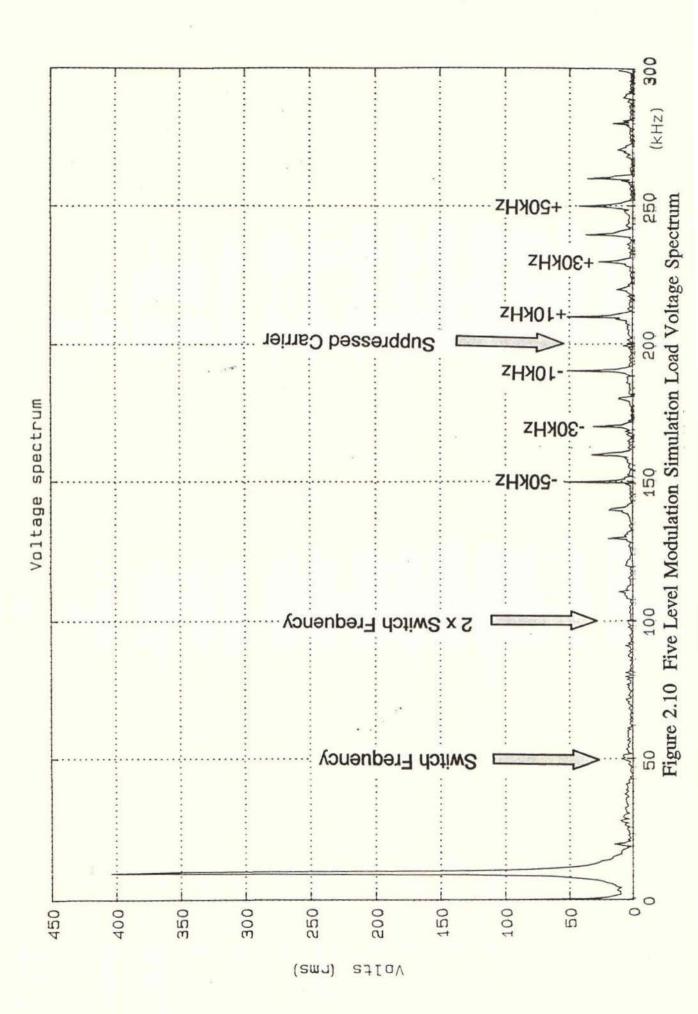

| Figure 2.10 | Five Level Modulation Similation Voltage<br>Spectrum                                            | 26   |

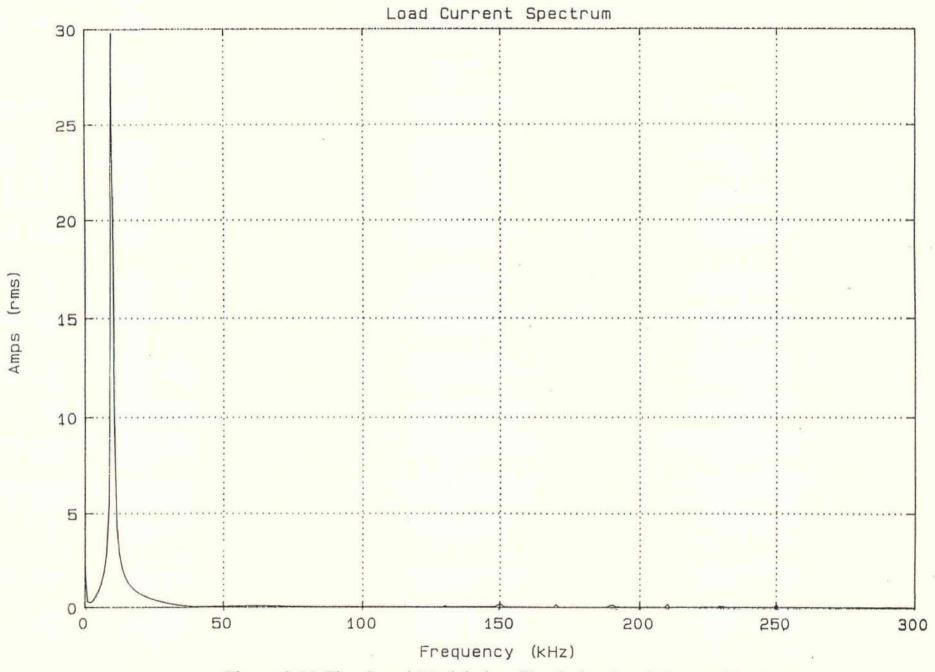

| Figure 2.11 | Five Level Modulation Simulation Load<br>Current Spectrum                                       | 27   |

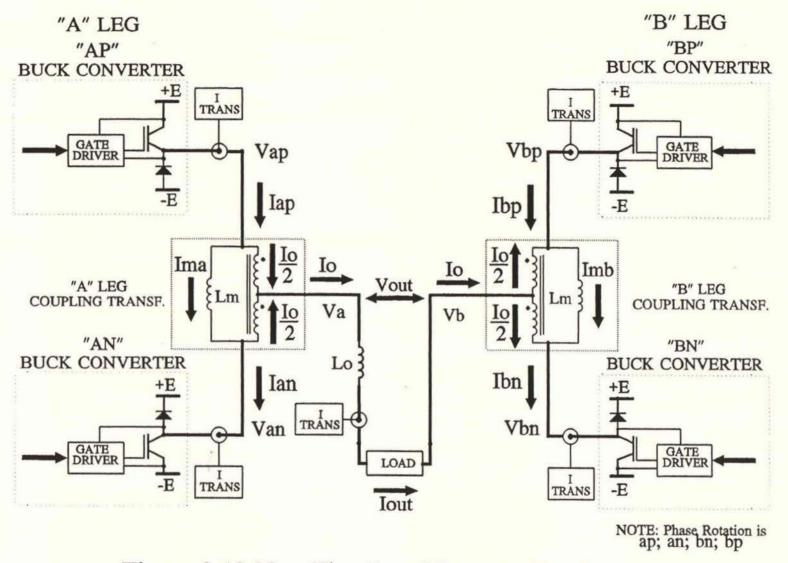

| Figure 2.12 | New Five Level Inverter Topology                                                                | 29   |

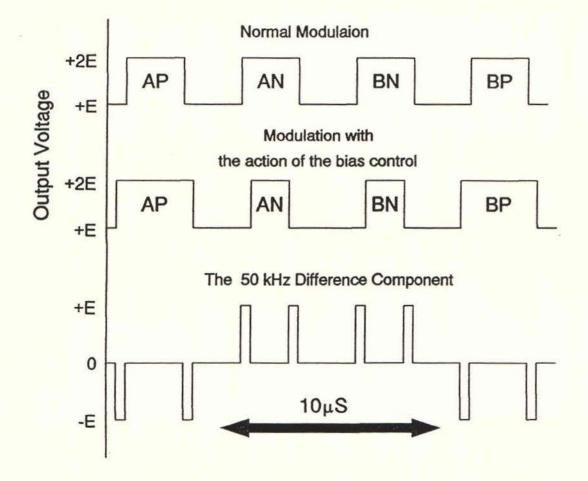

| Figure 2.13 | The Effect of Bias Current Control on<br>the Modulation Integrity                               | 33   |

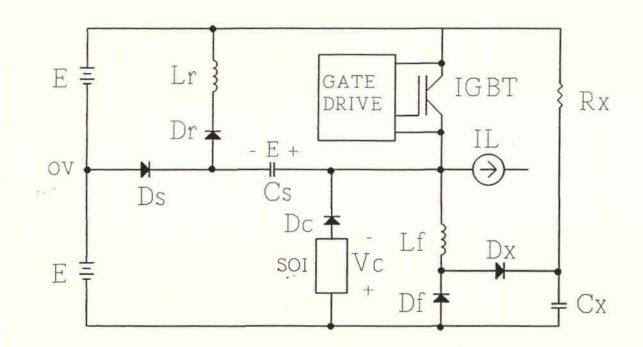

| Figure 2.14 | Simplified Positive Buck Converter Cell                                                         | 36   |

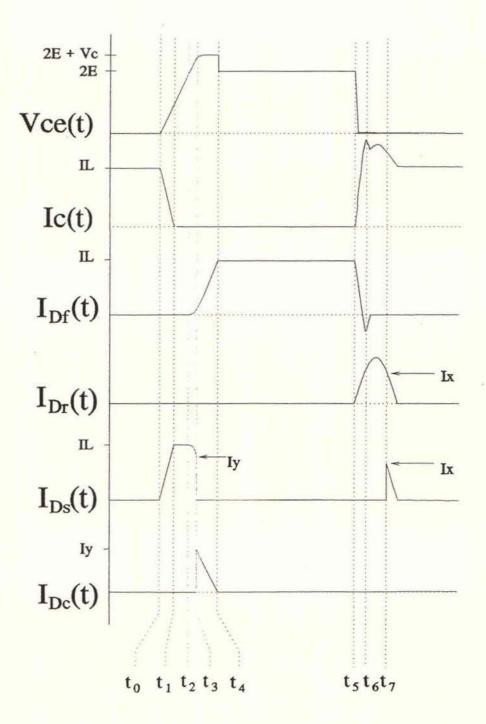

| Figure 2.15 | Positive Buck Converter Cell Waveforms                                                          | 40   |

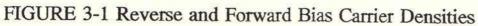

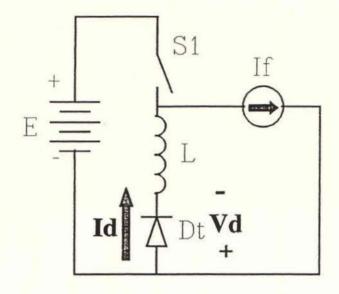

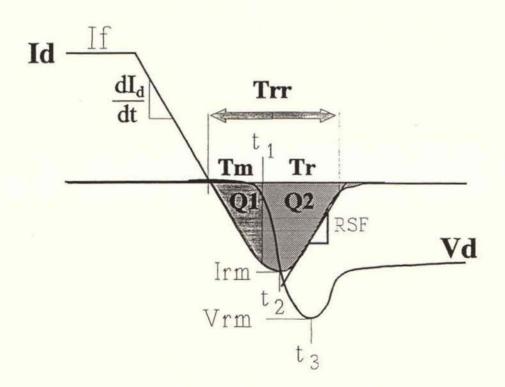

| Figure 3.1  | Reverse and Forward Bias Carrier<br>Densities                                                   | 45   |

| Figure 3.2  | Power Diode Reverse Recovery Transient                                                          | 51   |

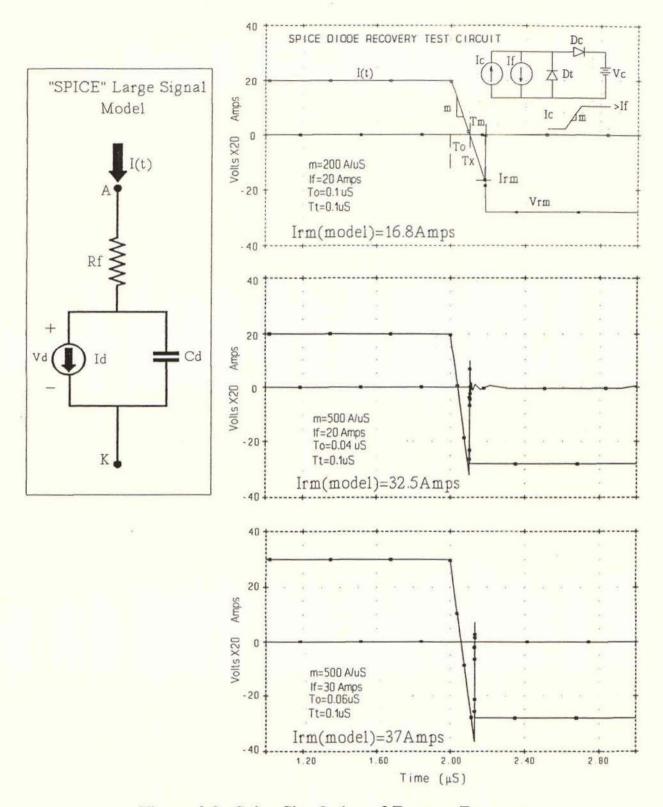

| Figure 3.3  | Spice Simulation of Reverse Recovery                                                            | 56   |

| Figure 3.4  | Minority Carrier Life Time according to SPICE using Manufacturers Data                          | 61   |

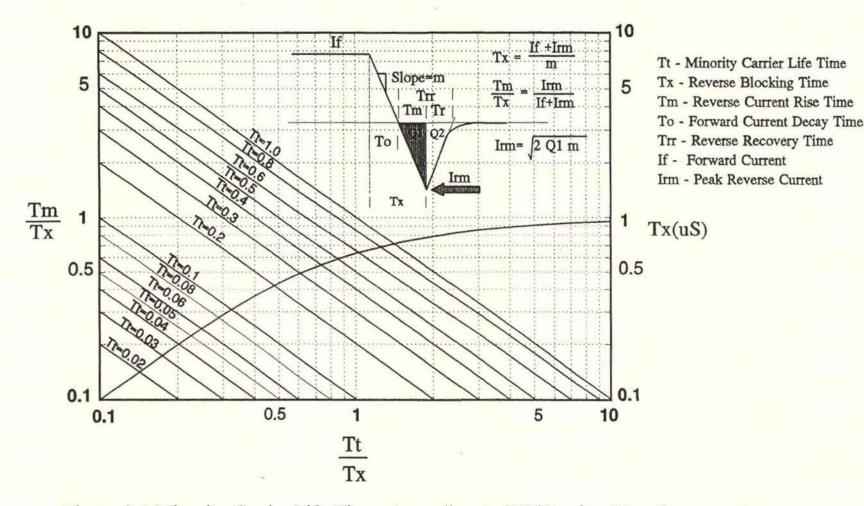

| Figure 3.5  | Determination of I <sub>rm</sub> according to SPICE                                             | 63   |

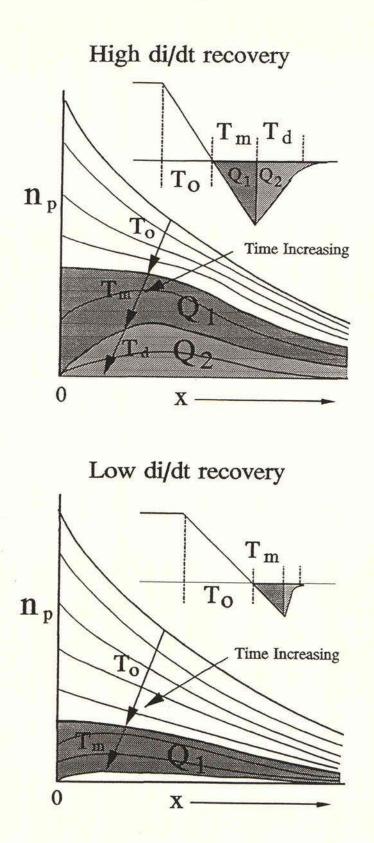

| Figure 3.6  | Excess Minority Carrier Concentration<br>during Reverse Recovery                      | 65  |

|-------------|---------------------------------------------------------------------------------------|-----|

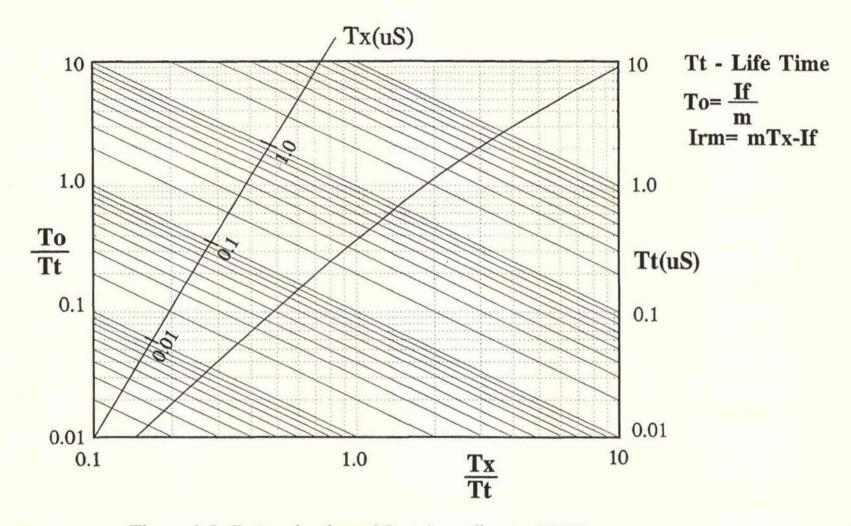

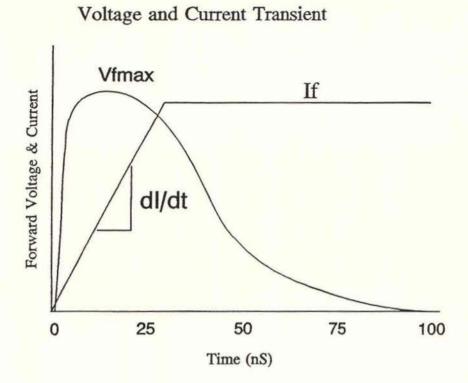

| Figure 3.7  | Minority Carrier Lifetime according to<br>Modified Model using Manufacturer's Data    | 70  |

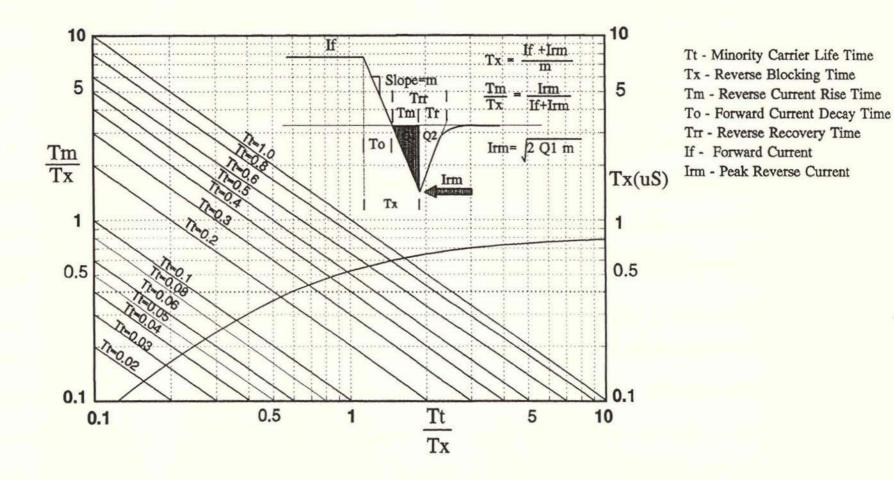

| Figure 3.8  | Determination of Irm using Modified Model                                             | 71  |

| Table 3.1   | Power Diode Reverse Recovery Lookup Table                                             | 72  |

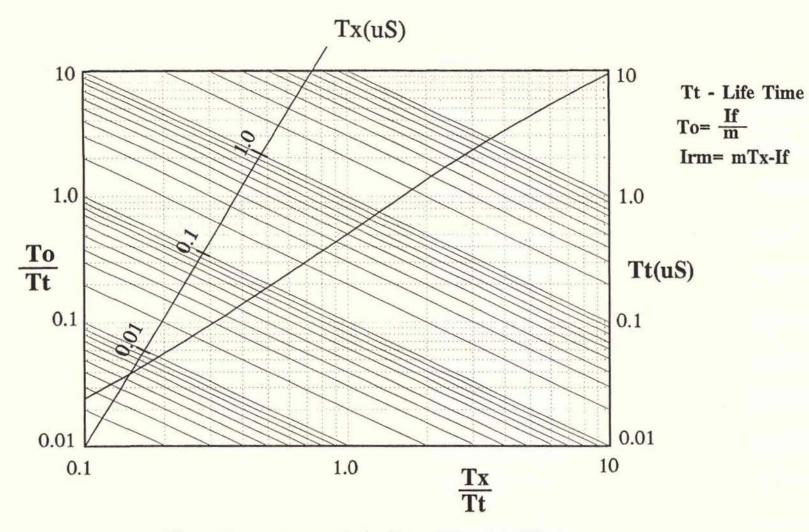

| Figure 3.9  | Commercial Diode Verses Model Comparison                                              | 73  |

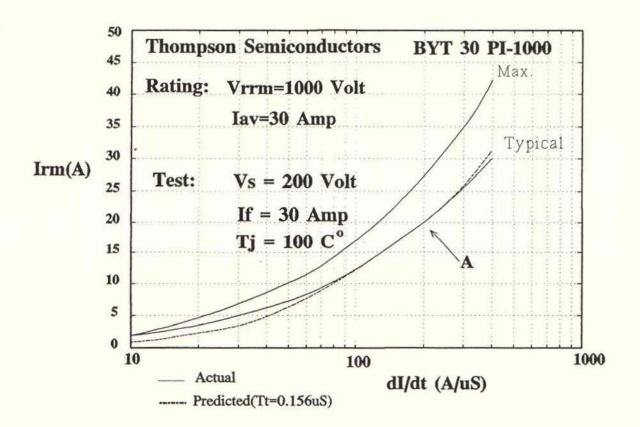

| Figure 3.10 | Typical Diode Forward Recovery Transient                                              | 78  |

| Figure 3.11 | Circuit Effects of Diode Forward Recovery                                             | 81  |

| Figure 3.12 | Insulated Gate Bi–Polor Transistor<br>Operation                                       | 86  |

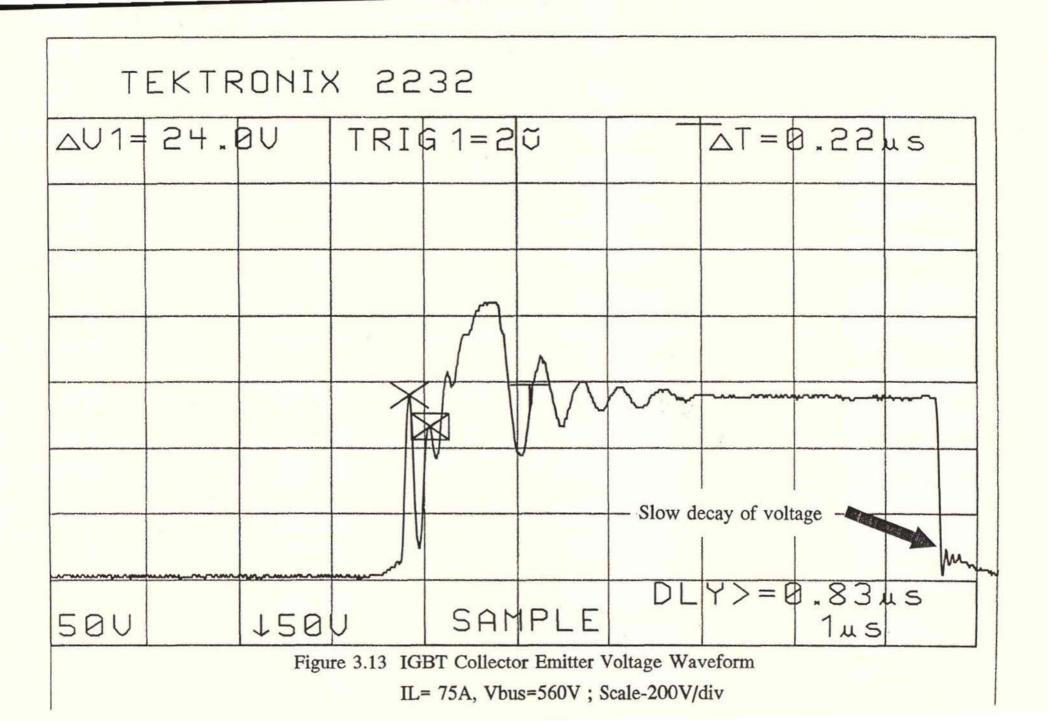

| Figure 3.13 | IGBT Collector Emitter Voltage Waveform                                               | 90  |

| Figure 4.1  | Simplified Positive Buck Converter Cell                                               | 96  |

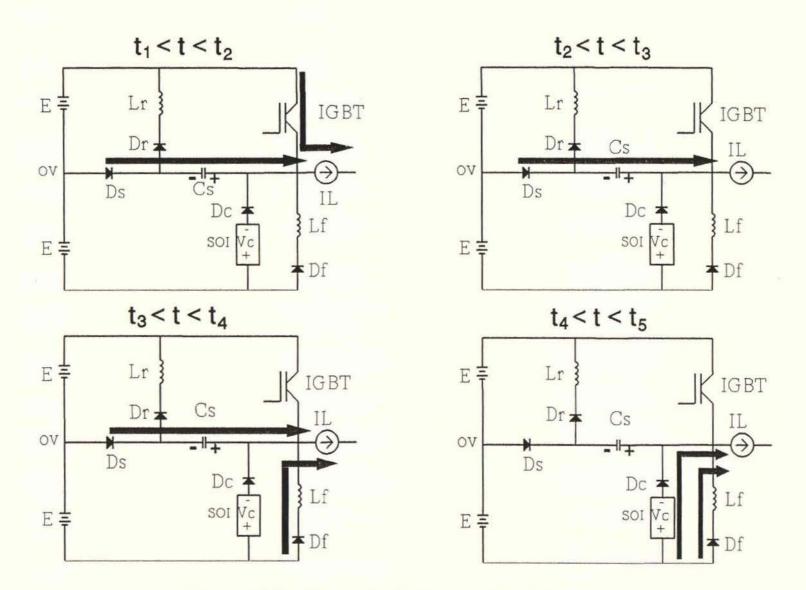

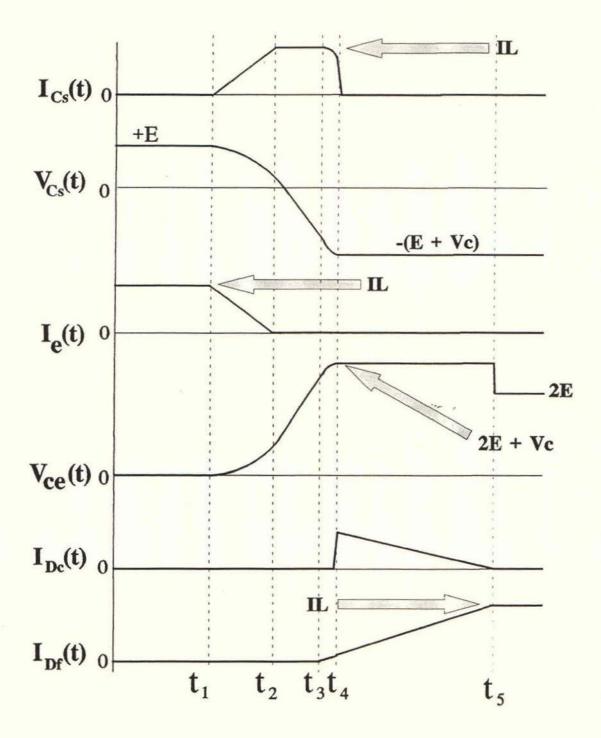

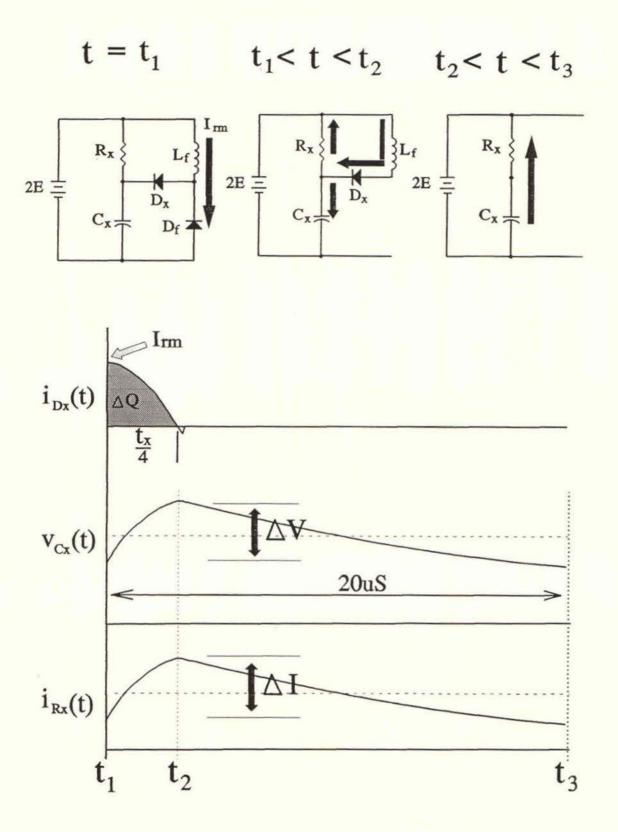

| Figure 4.2  | Snubber and Clamp Operational Sequence                                                | 99  |

| Figure 4.3  | Snubber and Clamp Waveforms                                                           | 100 |

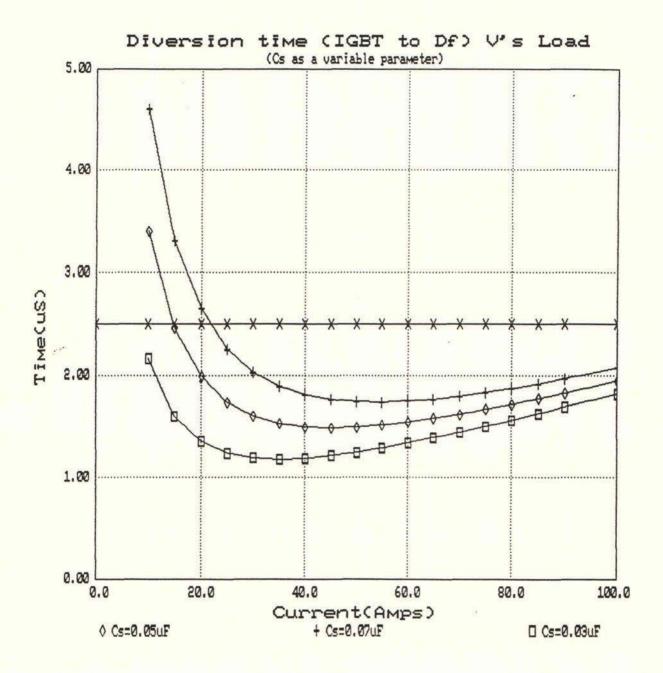

| Figure 4.4  | Effect of $C_s$ on the Total IGBT to $D_f$<br>Diversion Time                          | 109 |

| Table 4.1   | Diode $D_s$ Junction Temperature for $C_s$<br>Equal to $0.03_1 0.05$ and $0.07 \mu F$ | 113 |

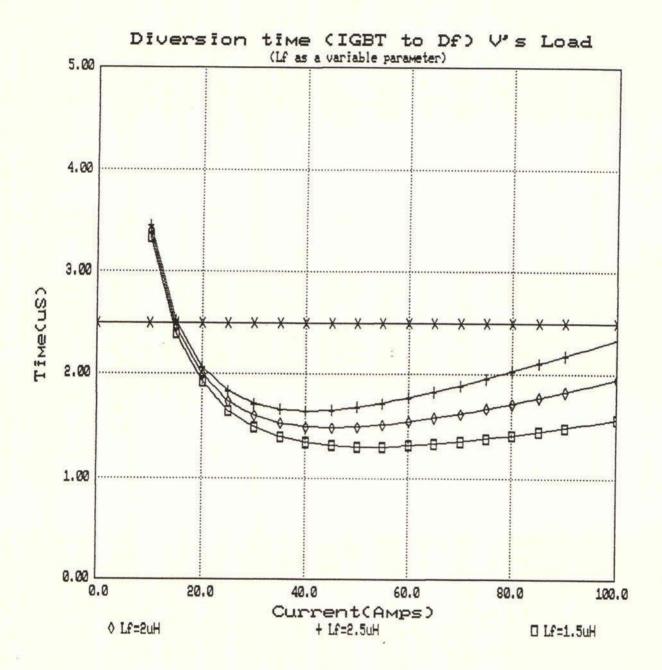

| Figure 4.5  | Effect of L <sub>f</sub> on the Total IGBT to D <sub>f</sub><br>Diversion Time        | 114 |

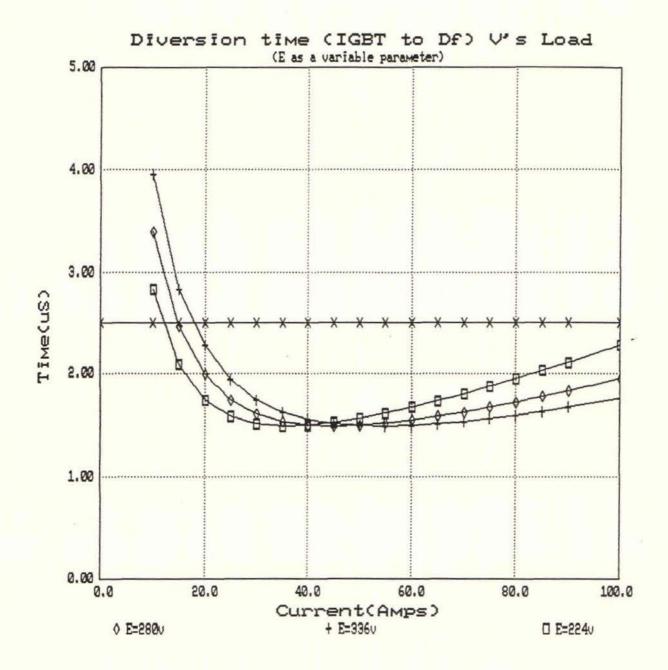

| Figure 4.6  | Effect of the Bus Voltage on the Total<br>IGBT to D <sub>f</sub> Diversion Time       | 116 |

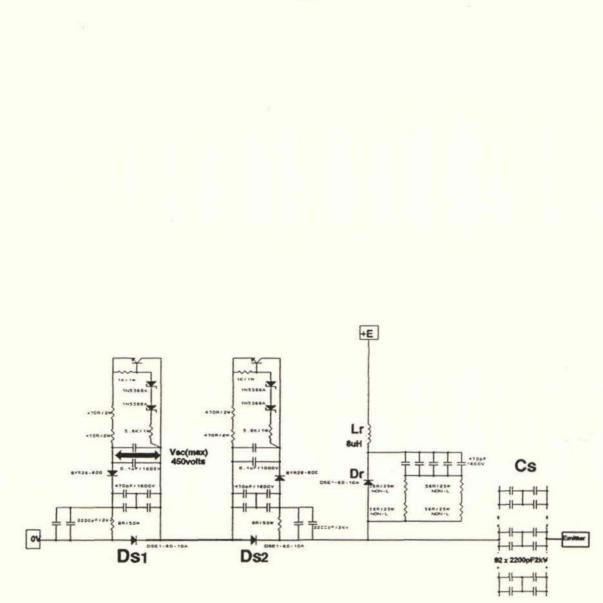

| Figure 4.7  | Snubber Module Schematic                                                              | 121 |

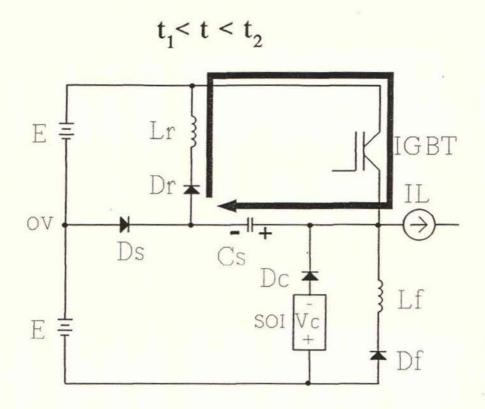

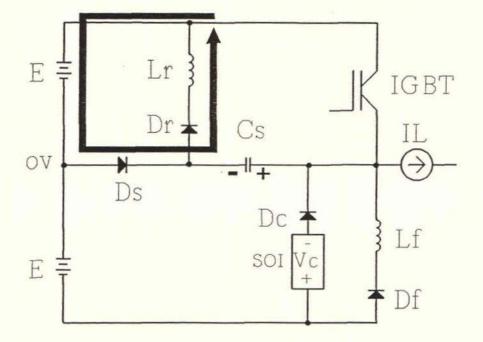

| Figure 4.8  | Resonant Reversal Operation                                                           | 122 |

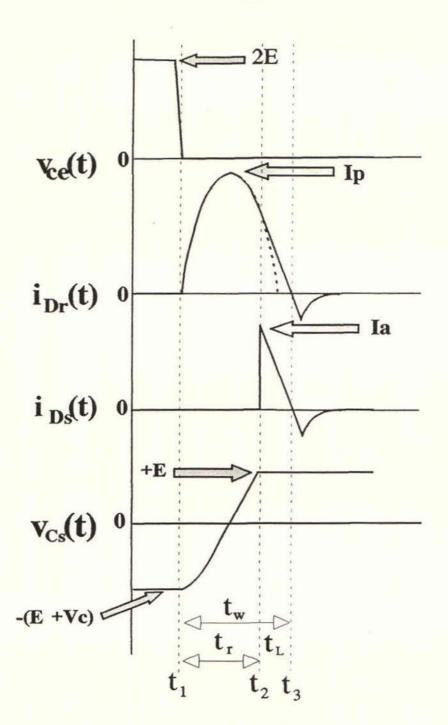

| Figure 4.9  | Snubber Resonant Reversal Waveforms                                                   | 123 |

| Figure 4.10 | Clamp Module Schematic                                                                | 136 |

| Figure 4.11 | 500 Watt Self Oscillating Inverter<br>Schematic                                       | 137 |

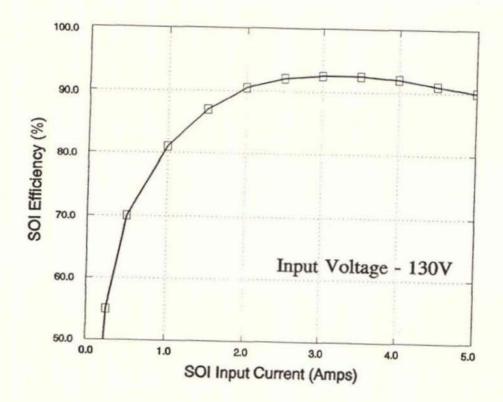

| Figure 4.12 | SOI Efficiency as a Function of Input<br>Current                                      | 141 |

| Figure 4.13 | Freewheel Diode Module Schematic                                                      | 143 |

| Figure 4.14 | Voltage Clamping Action of $C_x$ and $R_x$                                            | 148 |

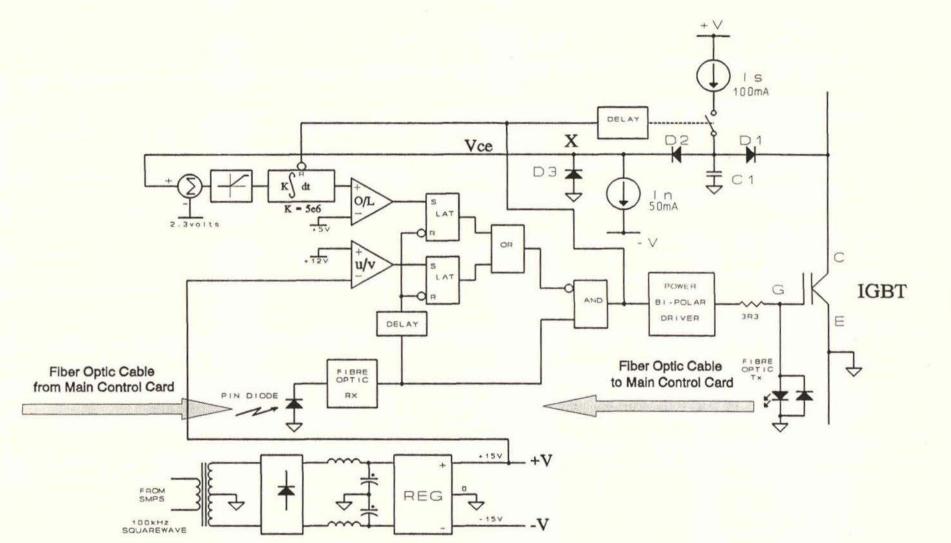

| Figure 4.15 | Gate Driver Block Diagram                                                             | 156 |

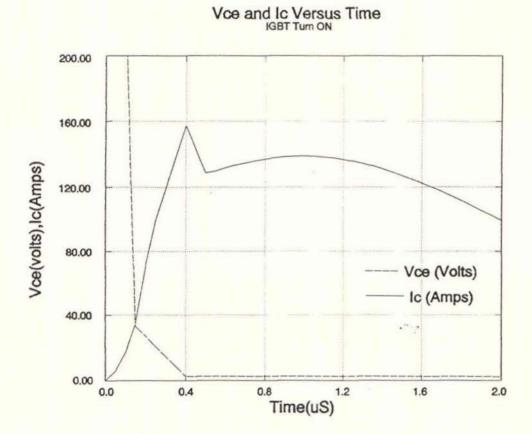

| Figure 4.16 | Predicted IGBT Voltage and Current during<br>Turn On                   | 160 |

|-------------|------------------------------------------------------------------------|-----|

| Table 4.2   | IGBT Turn On Power Dissipation Spreadsheet                             | 162 |

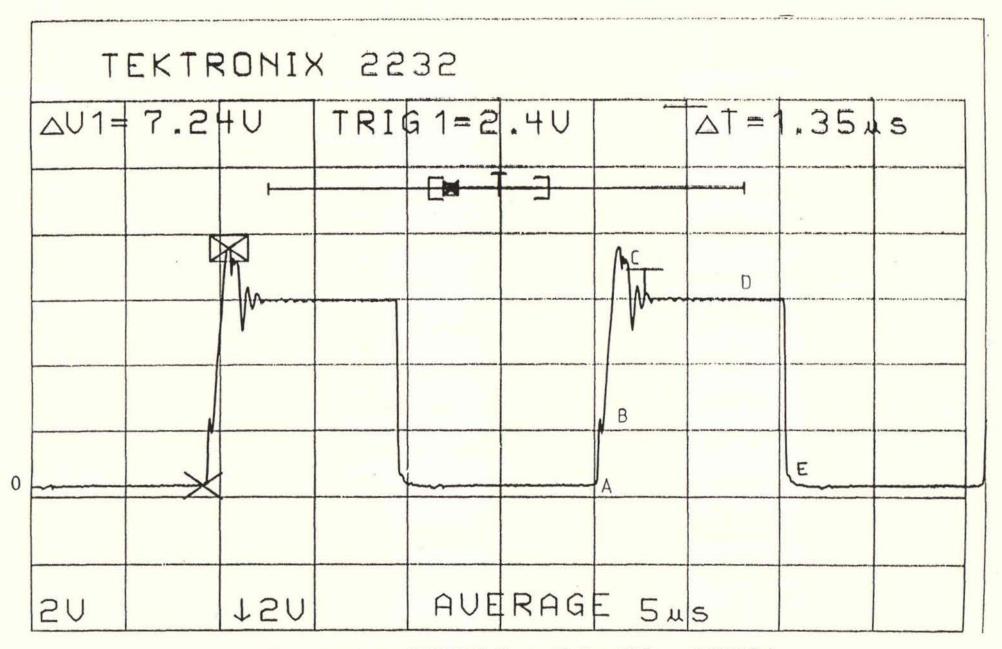

| Figure 4.17 | Actual IGBT Collector Emitter Voltage<br>(40A load)                    | 173 |

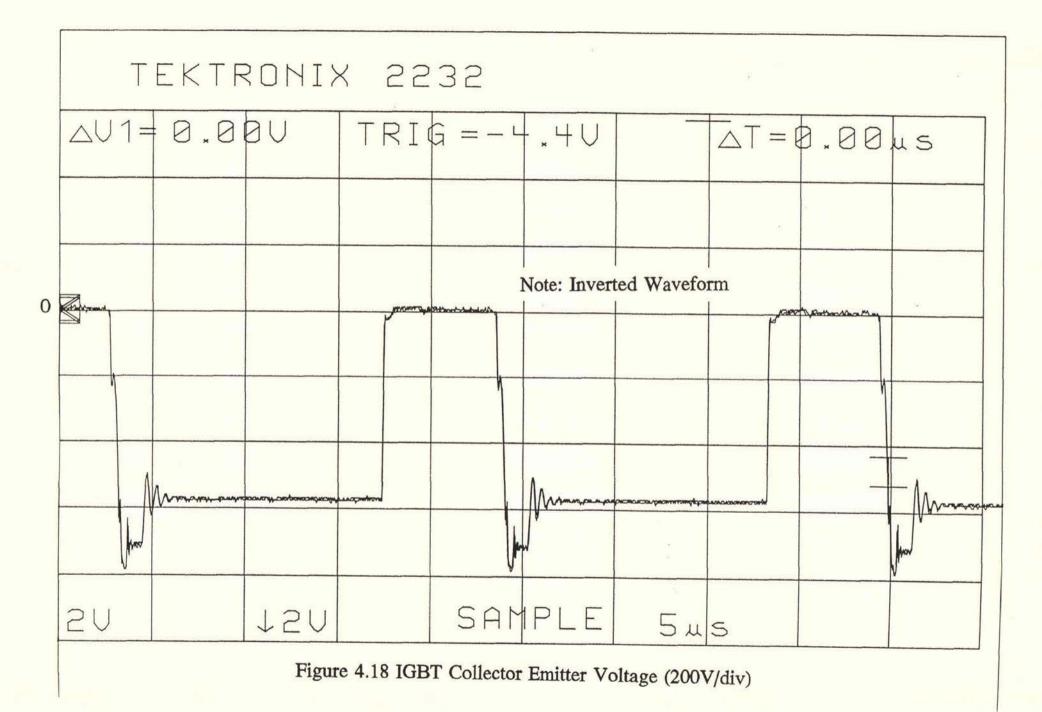

| Figure 4.18 | IGBT Collector Emitter Voltage (75A load)                              | 174 |

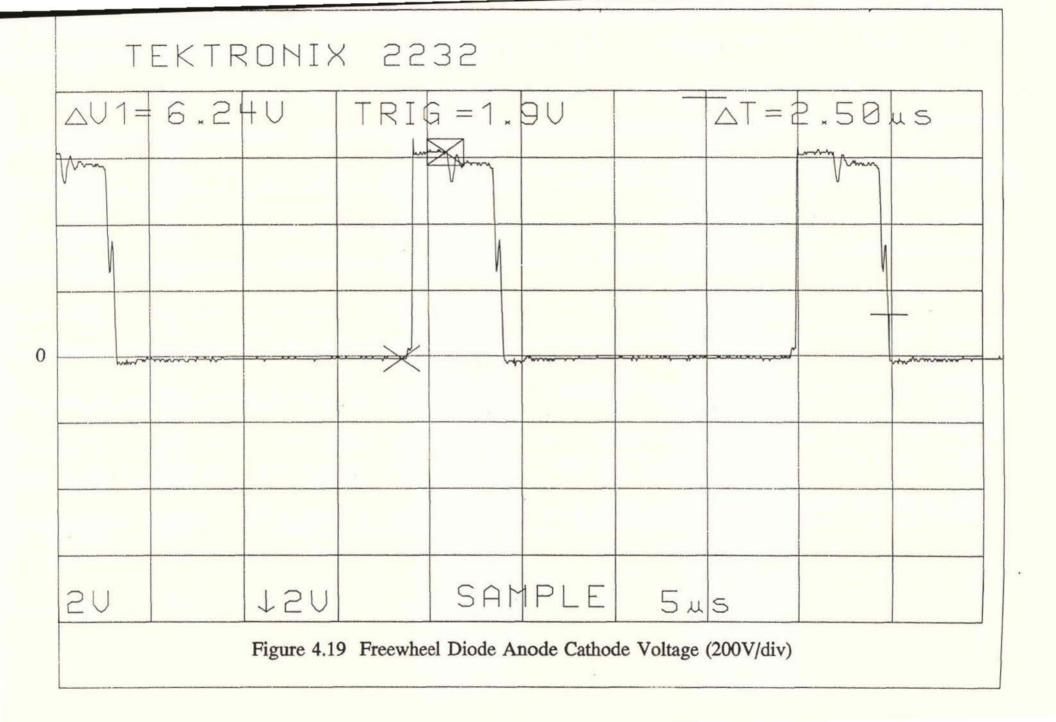

| Figure 4.19 | Freewheel Diode Anode Cathode Voltage                                  | 175 |

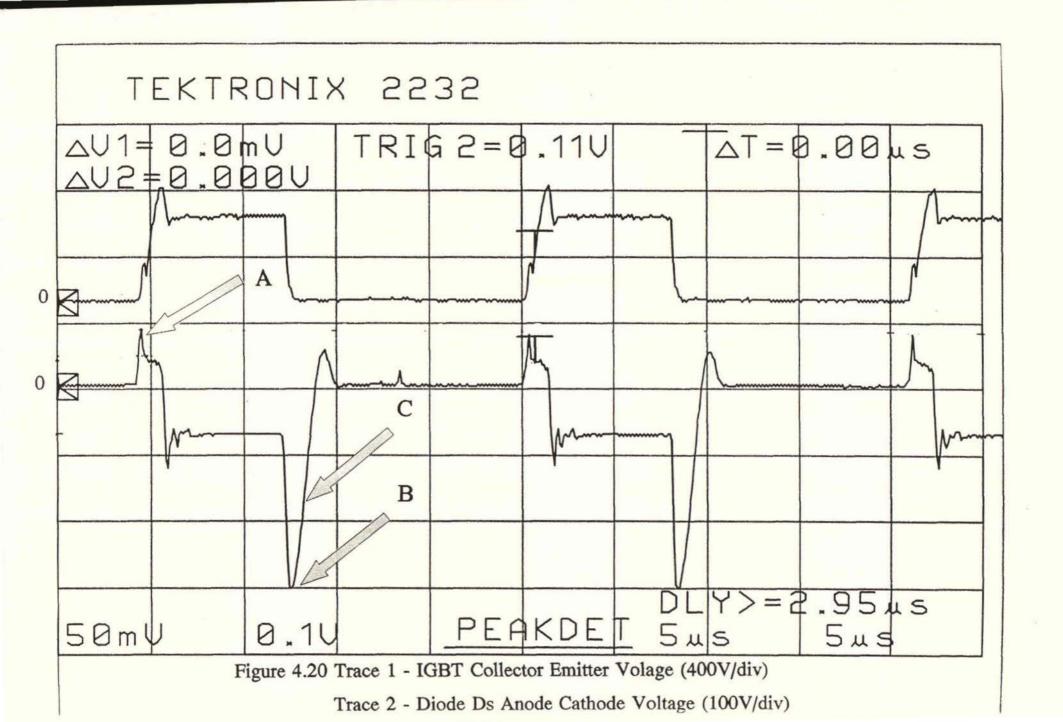

| Figure 4.20 | Diode D <sub>s</sub> Anode Cathode Voltage                             | 176 |

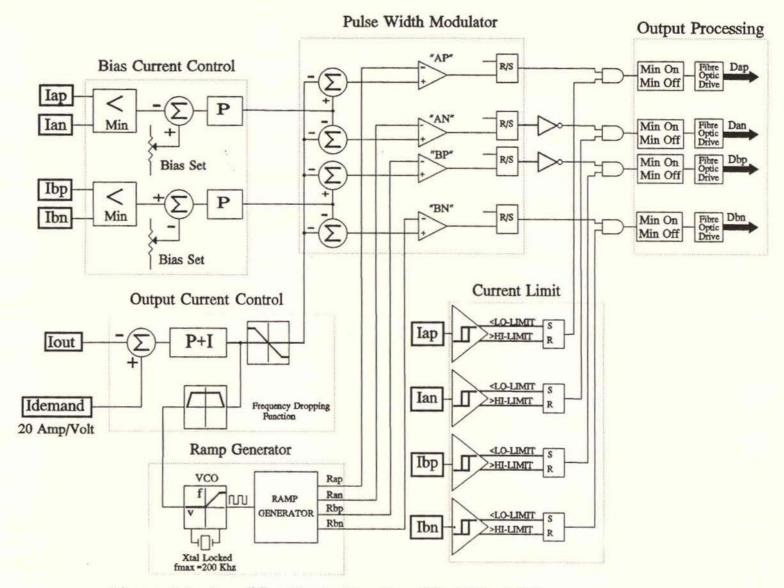

| Figure 5.1  | Amplifier Controller Simplified Block<br>Diagram                       | 178 |

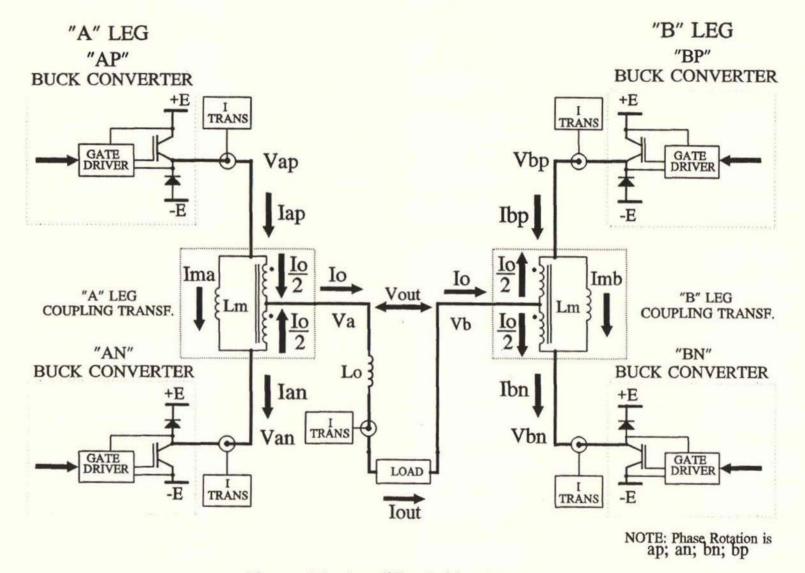

| Figure 5.2  | Amplifier Bridge Inverter                                              | 180 |

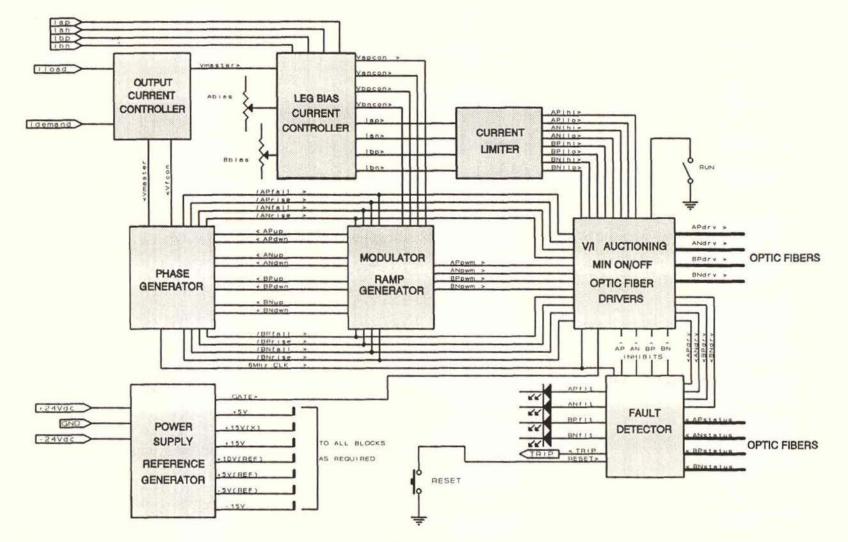

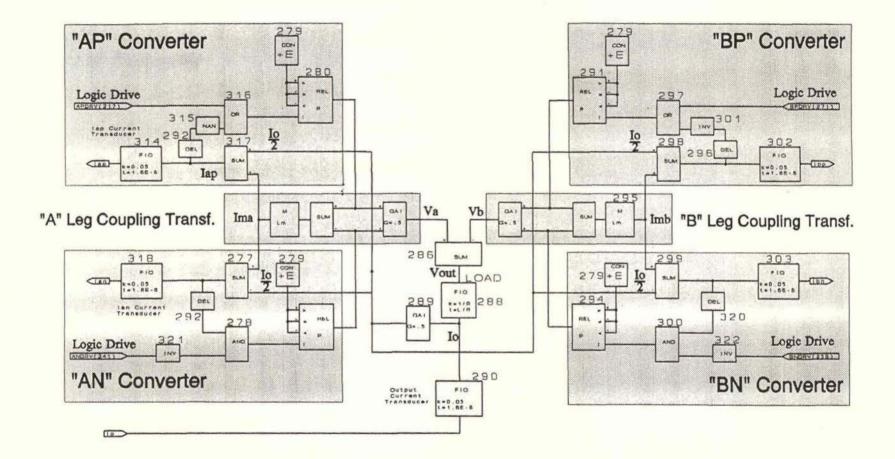

| Figure 5.3  | Controller System Overview                                             | 183 |

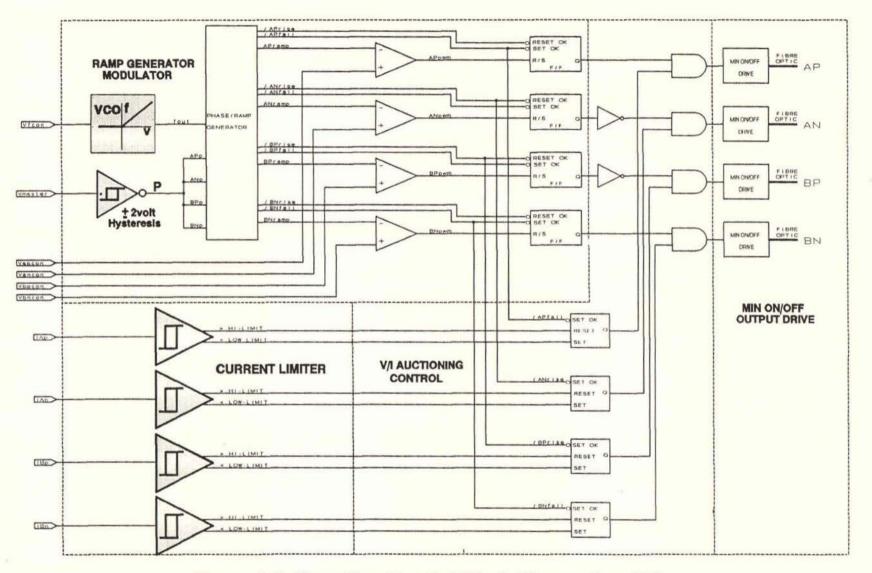

| Figure 5.4  | Controller Detailed Block Diagram Part "A"                             | 185 |

| Figure 5.5  | Controller Detailed Block Diagram Part "B"                             | 187 |

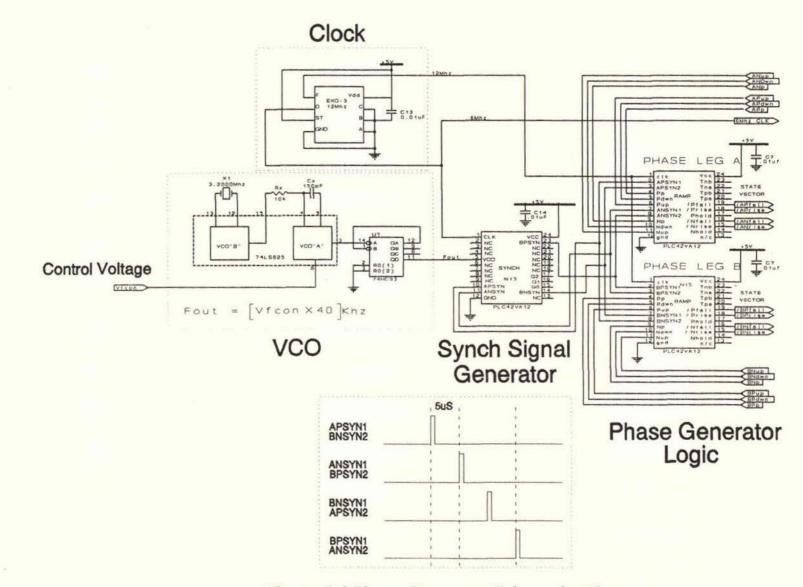

| Figure 5.6  | Phase Generator Schematic Diagram                                      | 188 |

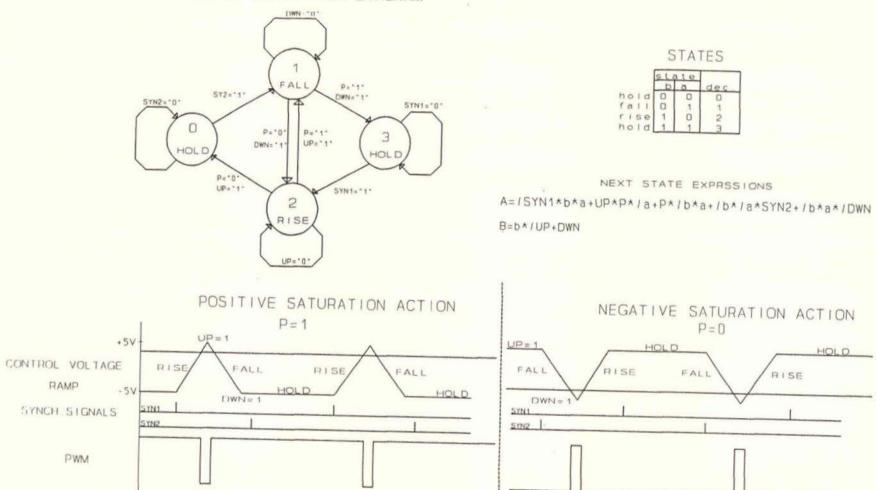

| Figure 5.7  | Phase Generator Logic Operation                                        | 191 |

| Figure 5.8  | Ramp Generator Analog Operation                                        | 192 |

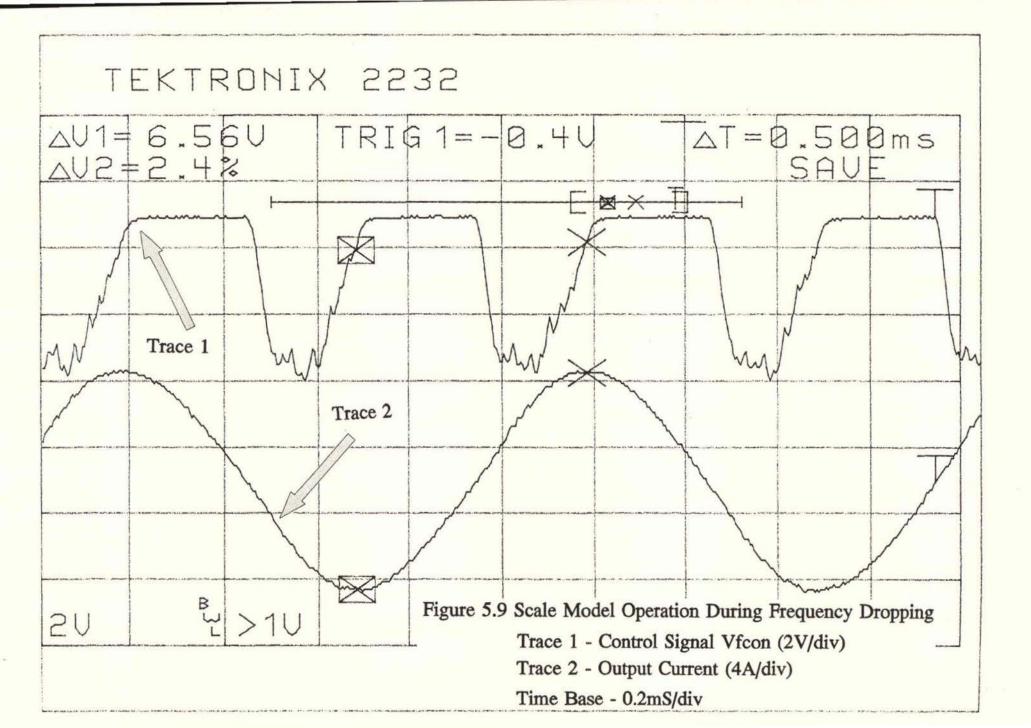

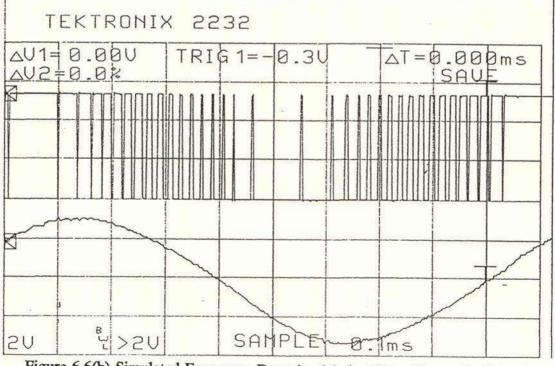

| Figure 5.9  | Scale Model Operation during Frequency<br>Dropping Part "A"            | 200 |

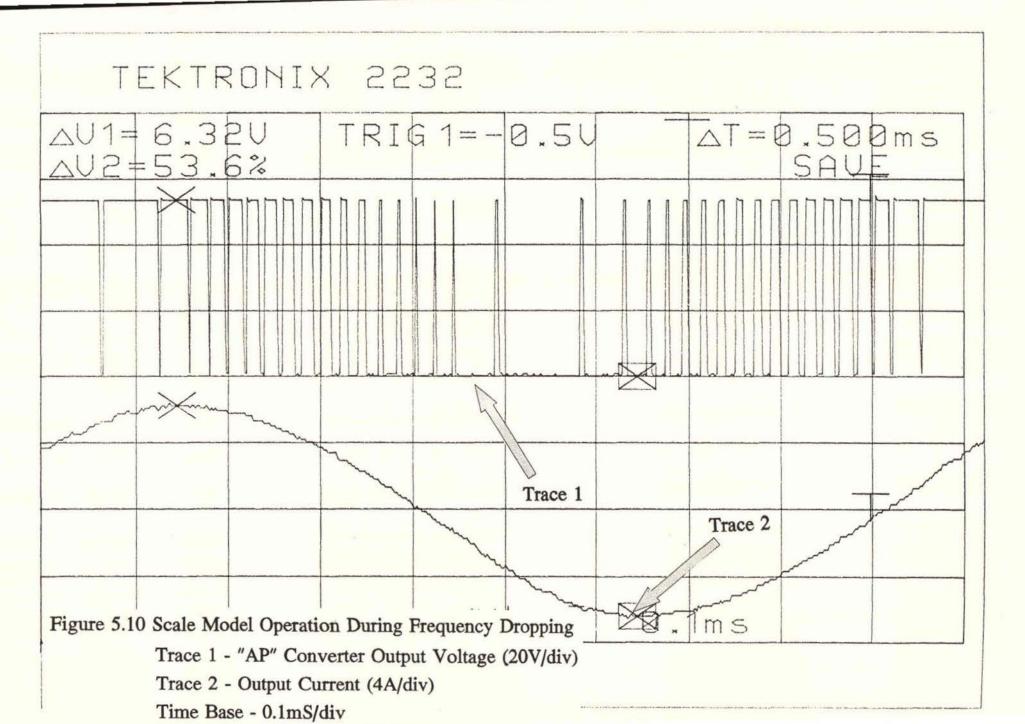

| Figure 5.10 | Scale Model Operation during Frequency<br>Dropping Part "B"            | 201 |

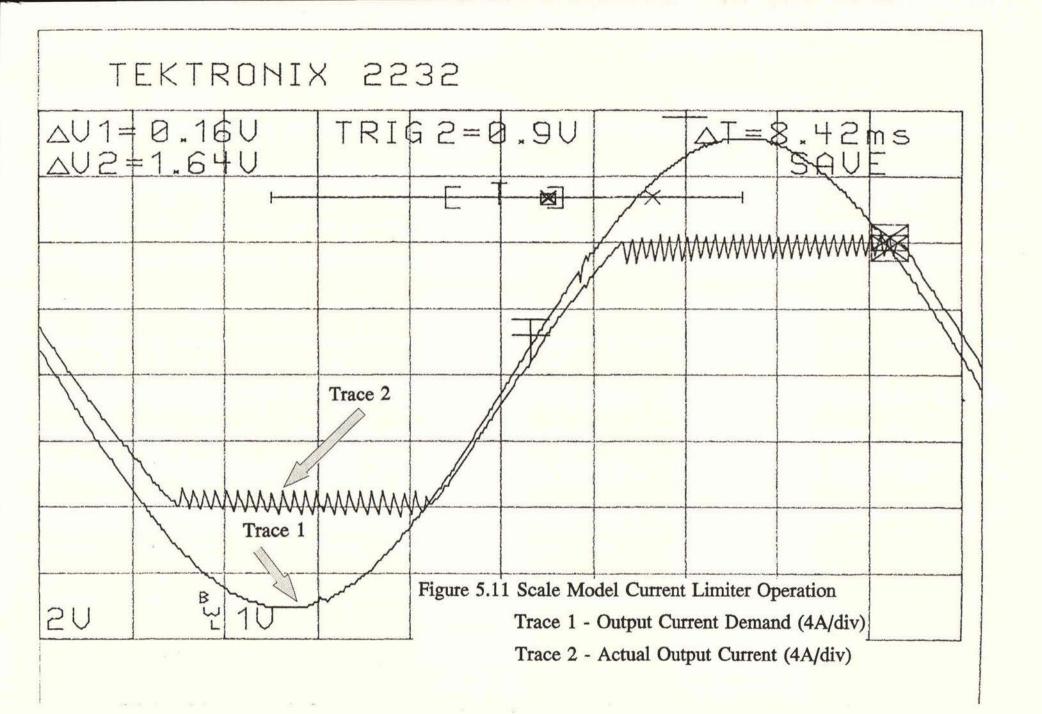

| Figure 5.11 | Scale Model Current Limited Operation                                  | 203 |

| Figure 5.12 | Amplifier Control System Block Diagram                                 | 205 |

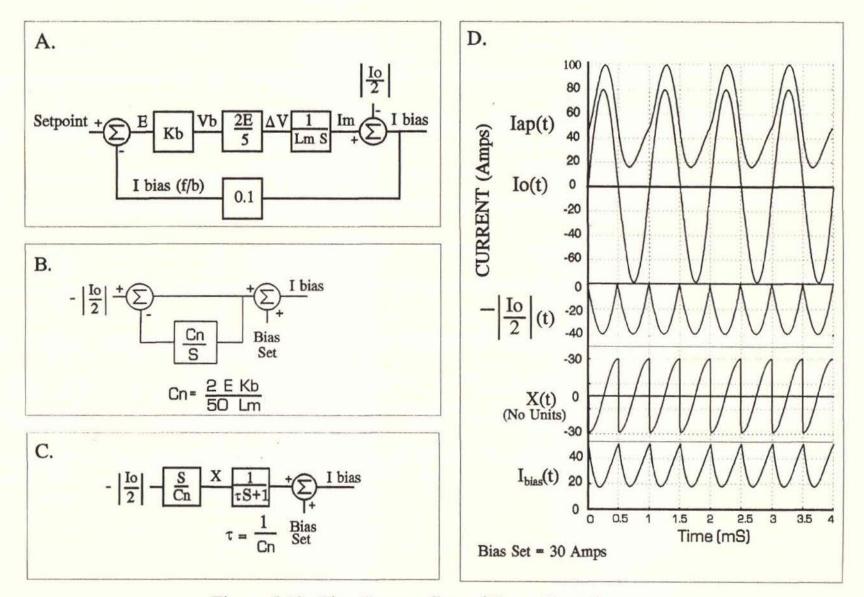

| Figure 5.13 | Bias Current Control Loop Operation                                    | 210 |

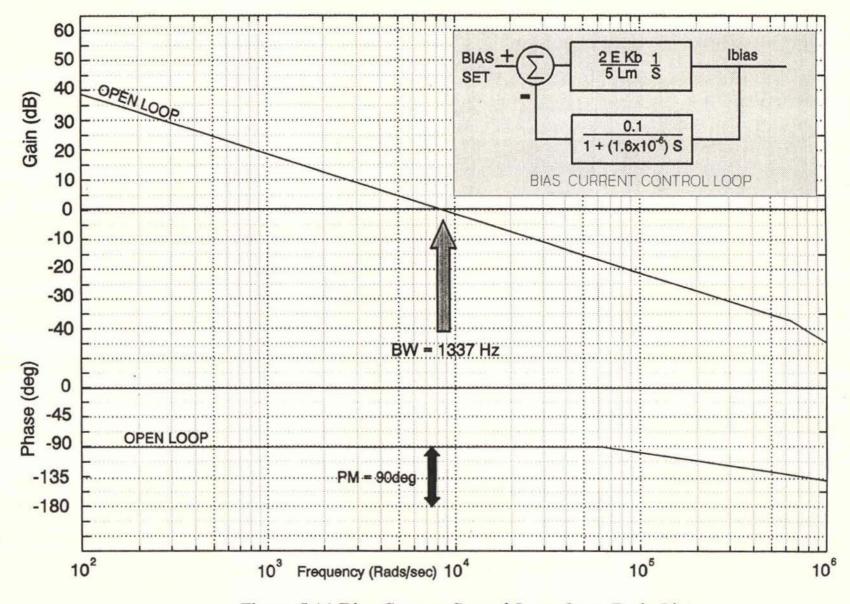

| Figure 5.14 | Bias Current Control Loop Open Loop Bode<br>Plot                       | 216 |

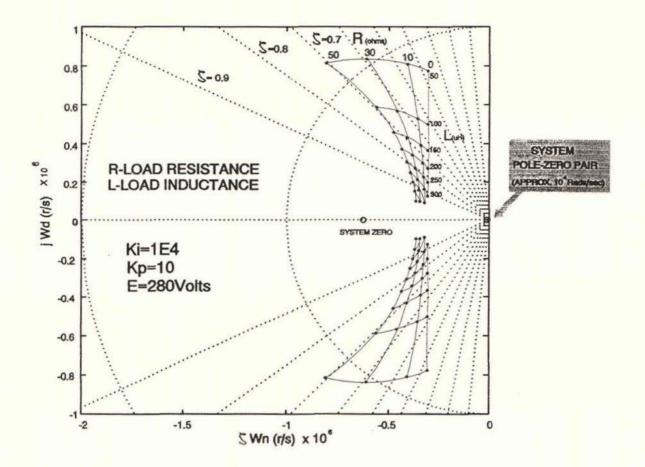

| Figure 5.15 | Output Current Control Loop Pole/Zero Map<br>Part "A"                  | 219 |

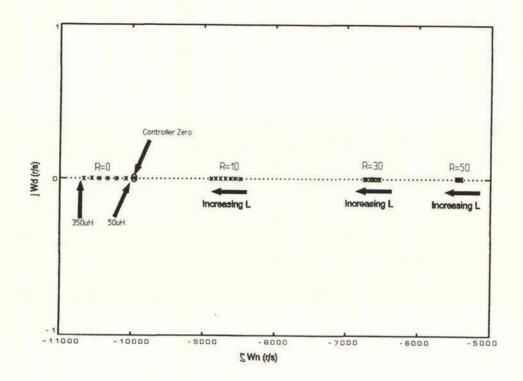

| Figure 5.16 | Output Current Control Loop Pole/Zero Map<br>Part "B"                  | 220 |

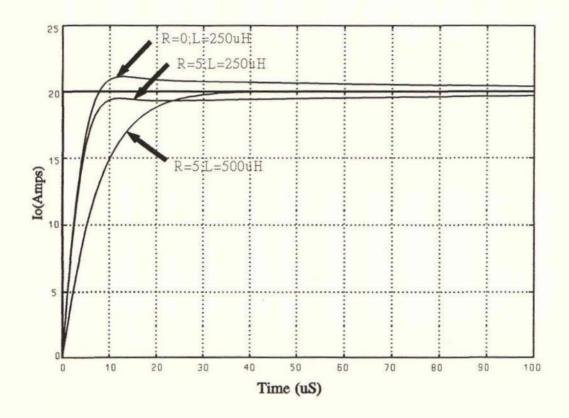

| Figure 5.17 | Output Current Control Loop Step Response                              | 223 |

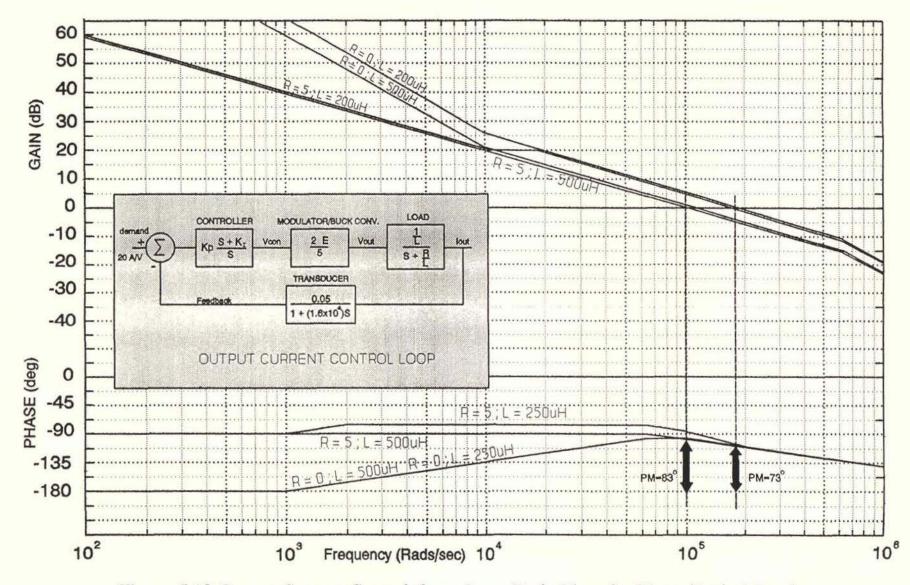

| Figure 5.18 | Output Current Control Open Loop Bode Plots<br>for Three Typical Loads | 244 |

| Figure 6.1  | "TUTSIM" Model of the Bridge Inverter                                  | 229 |

| Figure 6.2 | "TUTSIM" Model of the Analog Control<br>Section                                            | 231 |

|------------|--------------------------------------------------------------------------------------------|-----|

| Figure 6.3 | Simulated and Scale Model Output Voltage<br>for 10kHz Modulation                           | 233 |

| Table 6.1  | Output Voltage Spectrum                                                                    | 234 |

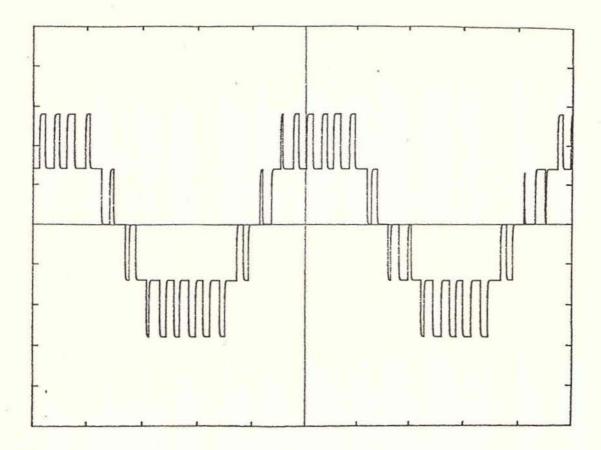

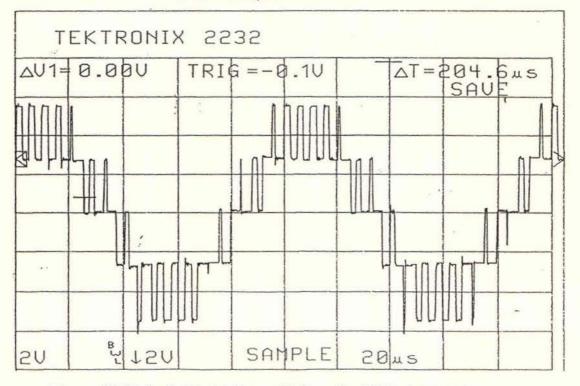

| Figure 6.4 | Scale Model Output Current for 10KHz<br>Modulation                                         | 235 |

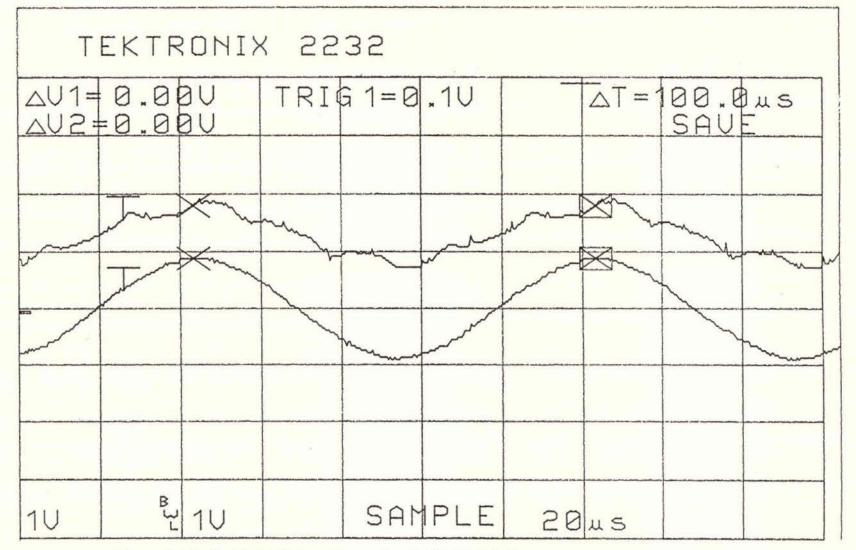

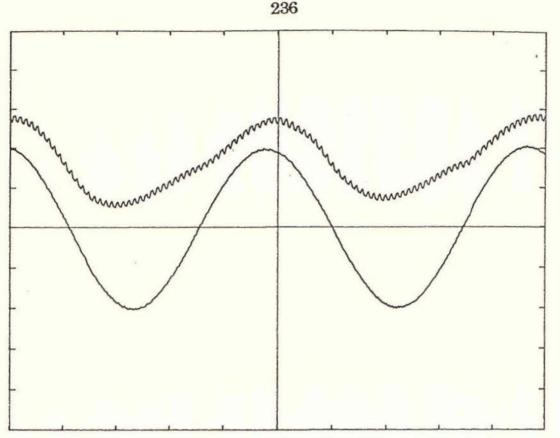

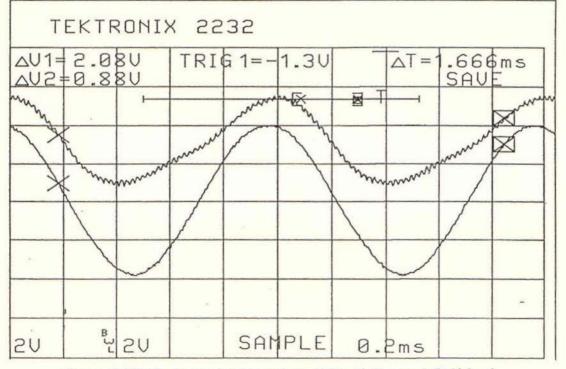

| Figure 6.5 | Simulated and Scale Model Operation;<br>1kHz, 56A <sub>rms</sub> , 1.5+2j Load             | 236 |

| Figure 6.6 | Simulated and Scale Model Frequency<br>Dropping Mode; 1kHz, 40A <sub>rms</sub> , 3+3j Load | 238 |

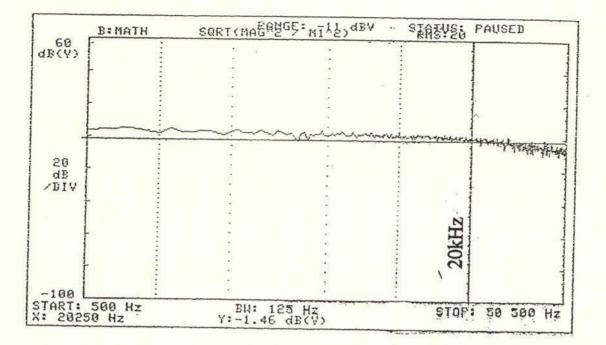

| Figure 6.7 | Scale Model Closed Loop Response; 5 ohm, 500 $\mu$ H Load                                  | 239 |

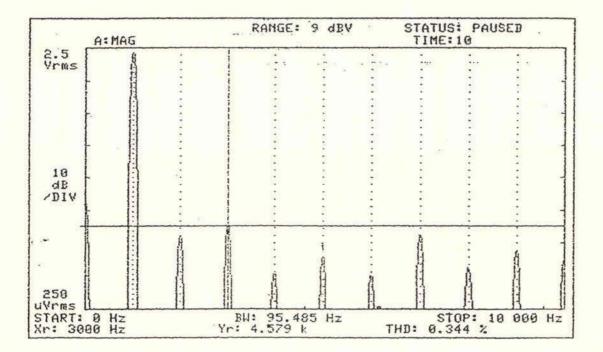

| Figure 6.8 | Scale Model Output Current Spectrum; 1kHz,<br>5A <sub>rms</sub> , 3+3j Load                | 240 |

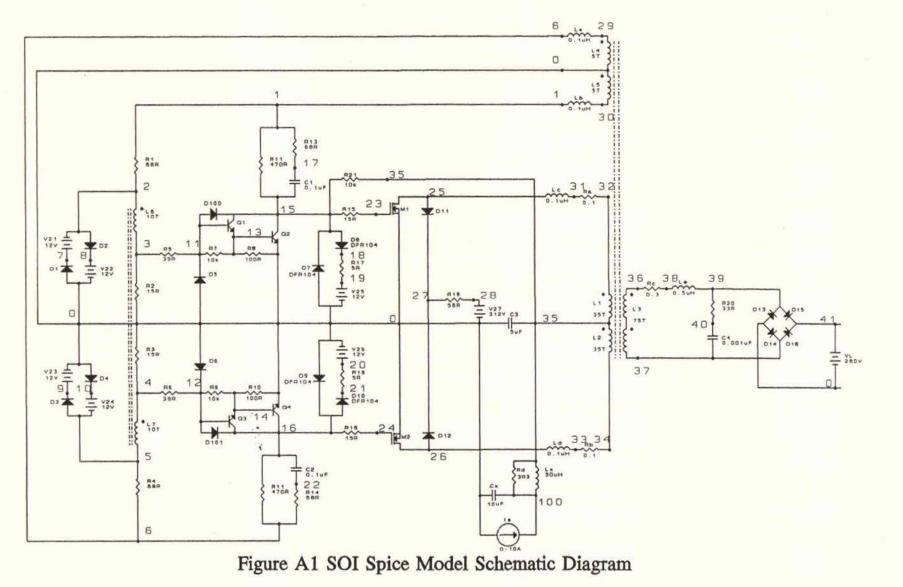

| Figure A1  | SOI Spice Model Schematic Diagram                                                          | 252 |

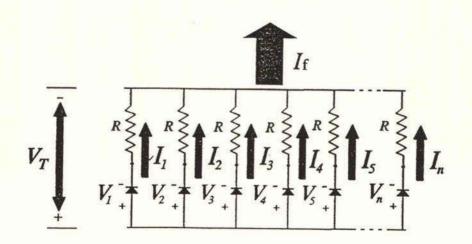

| Figure B1  | Parallel Diode Current Balance                                                             | 253 |

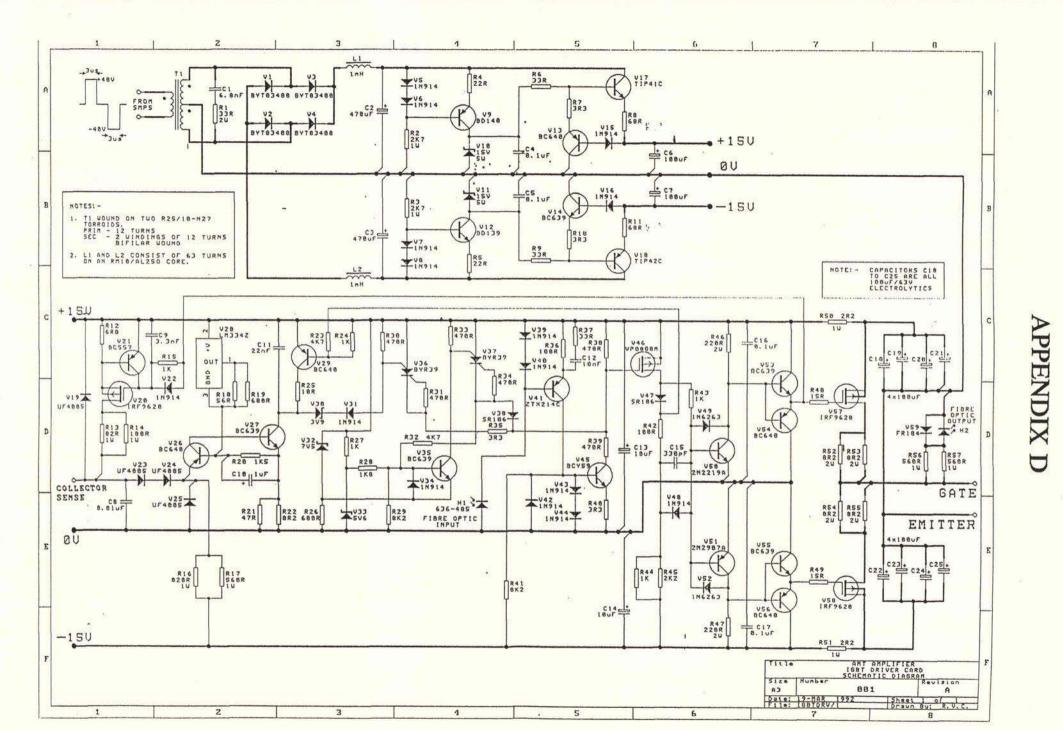

| Figure D1  | IGBT Driver Card Schematic Diagram                                                         | 257 |

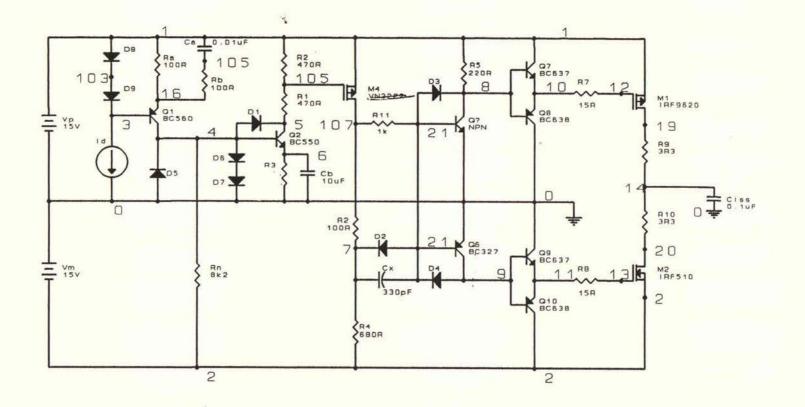

| Figure E1  | IGBT Drive Module Spice Model<br>Schematic Diagram                                         | 261 |

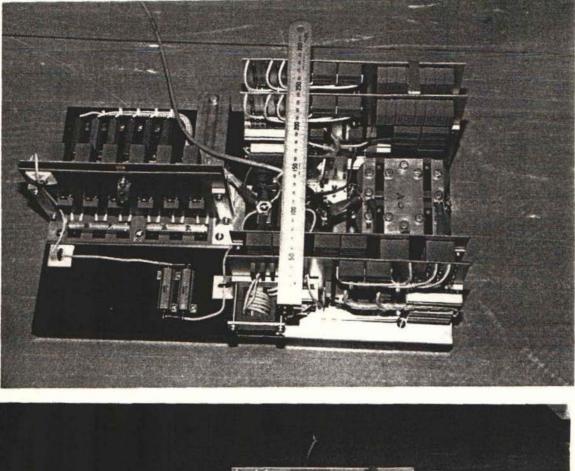

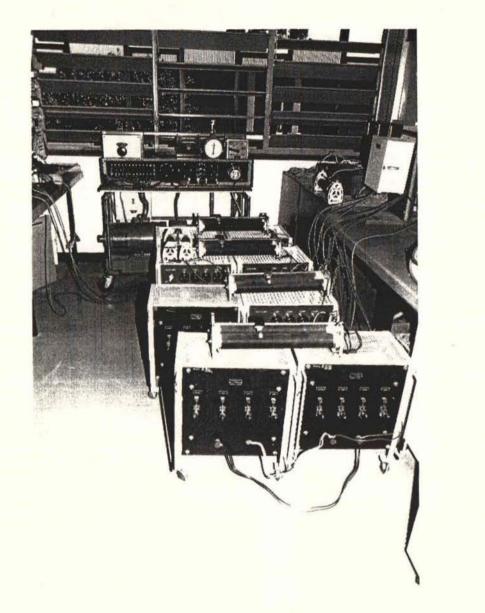

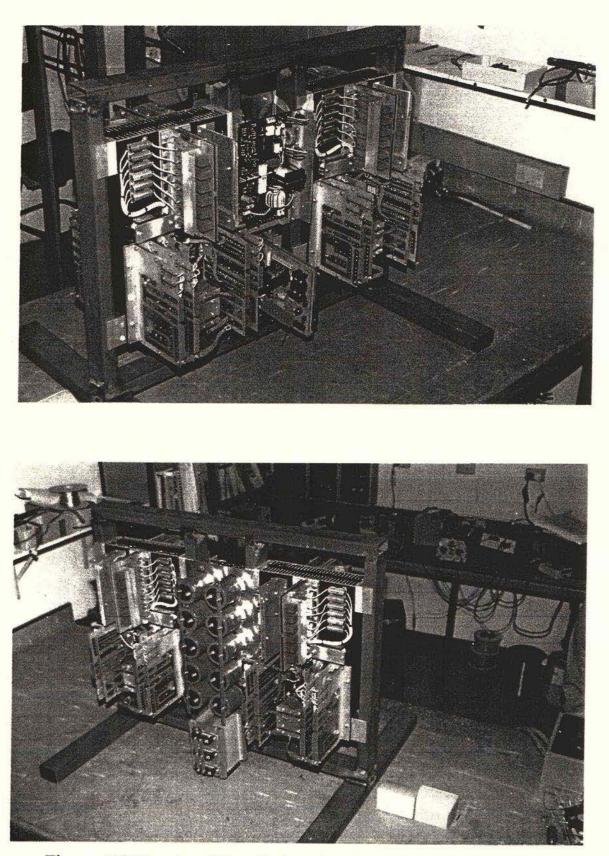

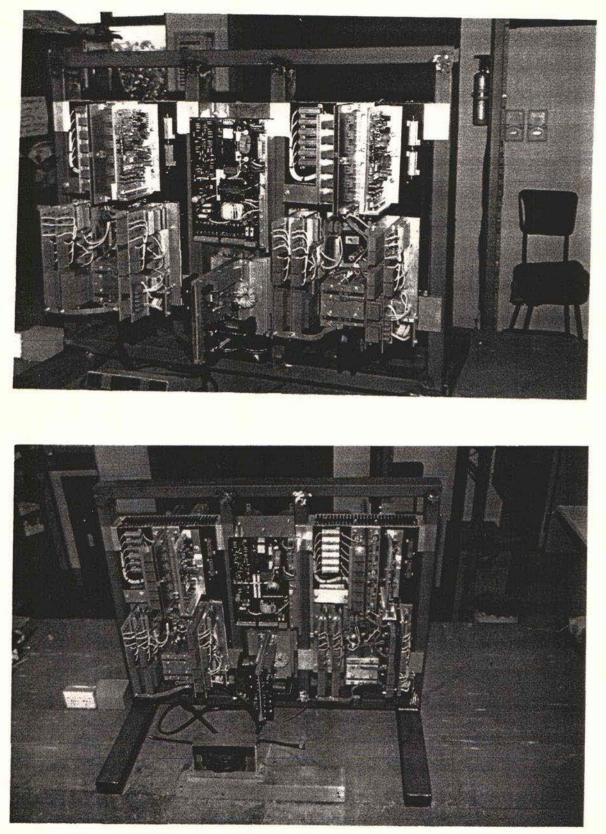

| Figure G1  | Positive Buck Converter Module<br>(Photograph)                                             | 263 |

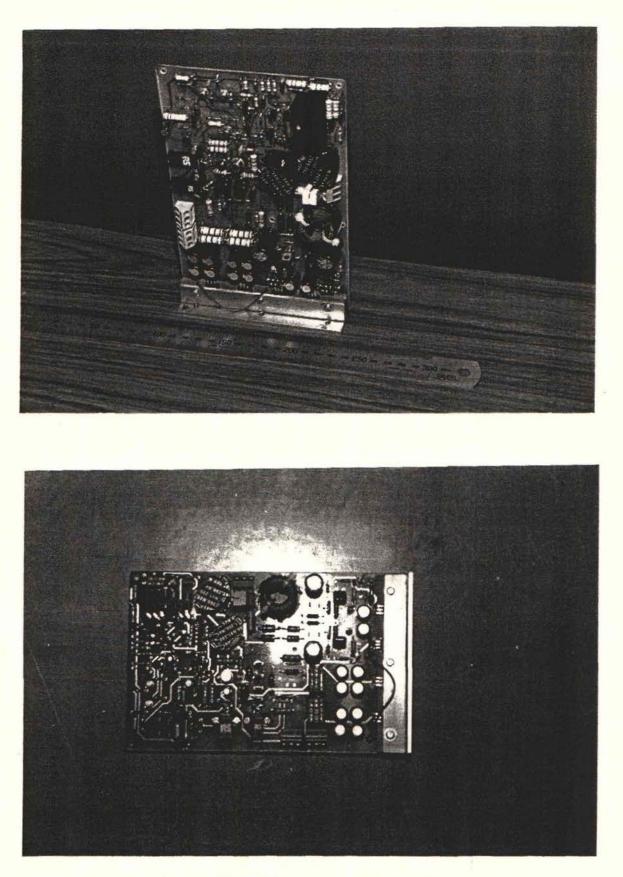

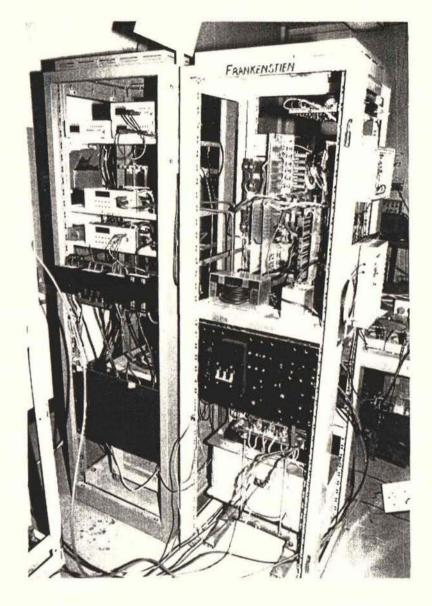

| Figure G2  | IGBT Gate Drive Module (Photograph)                                                        | 264 |

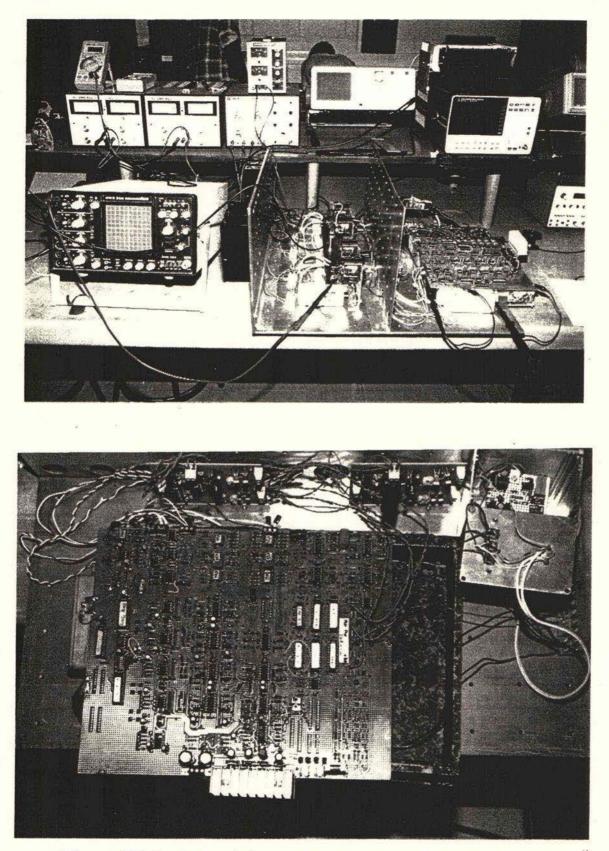

| Figure G3  | Self Oscillating Converter Module<br>(Photograph)                                          | 265 |

| Figure G4  | Buck Converter Test Installation and<br>Loading Bank (Photograph)                          | 266 |

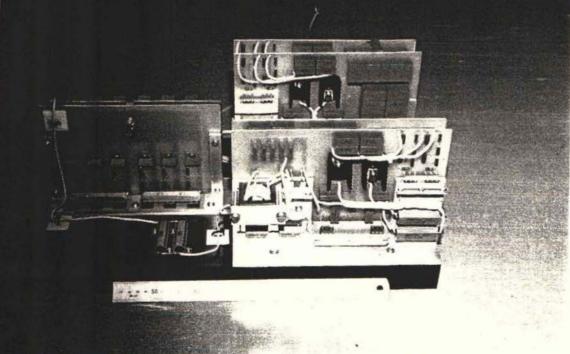

| Figure G5  | Scale Model Test Installation<br>and Controller PCB (Photograph)                           | 267 |

| Figure G6  | The Amplifier during the Construction<br>Phase (Photograph)                                | 268 |

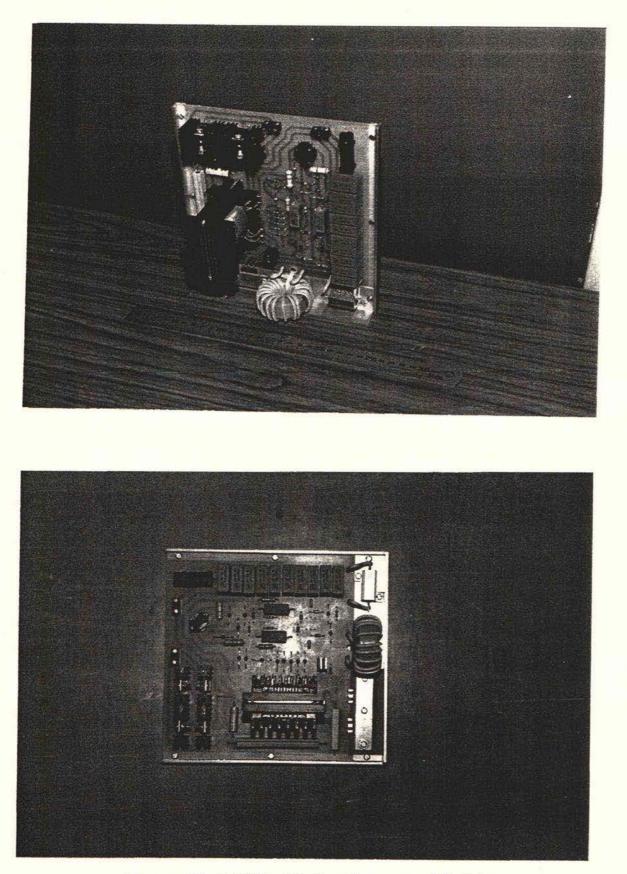

| Figure G7  | The Amplifier during the<br>Construction Phase (Photograph)                                | 269 |

### ACKNOWLEDGEMENTS

I wish to express my thanks to the staff of the Electrical Engineering Department at the University of Central Queensland for their support over the duration of this project. In particular I wish to acknowledge the contributions of my supervisors Dr. Peter Wolfs and Dr. Ken Kwong and the significant efforts made by Mr. Ken Best, Mr.Mike Gorman and the other technical staff of the Department.

### DECLARATION

The work contained in this thesis has not been previously submitted for a degree or diploma at any tertiary education institution. To the best of my knowledge this thesis contains no material previously published by another person except where due reference is made.

### Signature Redacted

Frank Flinders.

### PUBLICATIONS

The following publications have been produced during the course of this thesis

(i) P.J.Wolfs, F.M.Flinders, "An Improved Phase Leg", Australian Provisional Patent Specification No PK7430, 26<sup>th</sup> July 1991.

(ii) F.M. Flinders, P.J.Wolfs and K.Kwong, "An Improved Modulation Capability Inverter", Conference on Industrial Drives, University of Central Queensland, 18<sup>th</sup>-20<sup>th</sup> September 1991, pp 273-277.

(iii) F.M. Flinders, P.J.Wolfs and K.Kwong, "Prediction of Diode Reverse Recovery from Limited Data", AUPCEC 1992 Conference, Queensland University of Technology, 1<sup>st</sup>-2<sup>nd</sup> October 1992, pp 414-419.

(iv) F.M. Flinders, P.J. Wolfs, K.Kwong, "Improved techniques for Switching Power Amplifiers", James Goldstone School of Engineering Research Report Series, No. EE5, June 1992.

(v) F.M. Flinders, P.J. Wolfs, "A Charge Control Equation Based Method for Predicting Power Diode Reverse Recovery Behaviour", James Goldstone School of Engineering Research Report Series, No. EE6, August 1992.

Additionally the following paper has been accepted for publication in the IEEE Transactions on Power Electronics.

(vi) F.M.Flinders, P.J.Wolfs, K.Kwong, "Improved Techniques for Switching Amplifiers", IEEE Transactions on Power Electronics, Log No. #C182-HP-21, April 1992, accepted January 1993.

### 1. INTRODUCTION

This thesis covers the development of a 45kVA, 0-20kHz audio frequency switching amplifier. The project was supported by part of a NERDEC grant made to the University of Queensland for the development of a controlled source audiomagnetelluric, (CSAMT), system for geophysical exploration. The system is primarily targeted at economically exploitable mineral deposits and geophysical deposits associated with oil and gas fields, [1]. In the audiomagnetelluric system the region of earth of interest is illuminated using an artificial electromagnetic source. The surface electric and magnetic fields are measured at a distance in three orthogonal directions and the results recorded as impedances. The variation of input impedance with frequency is then used to construct a model for the depth resistivity structure. The nature of the underlying mineral deposits can be interpreted from this data.

The amplifier forms the artificial source in the system. The output current from the amplifier can be passed directly through the earth via two stakes. Alteratively the source can be coupled via a large diameter magnetic loop laid over the ground. The 45kVA switching amplifier is at present being constructed at the University of Central Queensland.

Although this amplifier was developed for a specific task its application is more broad ranging. Because the output waveform is of high quality up to a frequency of 10kHz it would be suitable as a modulator for shortwave and medium wave AM radio transmitters. Another important application is a source for driving electromagnetically driven shakers and vibrating tables. Because the output distortion is low the unit would also be ideal as a high power bass amplifier. It is also likely that the amplifier would be useful as standard equipment in scientific laboratories for conducting various physical experiments, [2]. In addition to the many applications for this amplifier there has also been several innovative techniques developed which will contribute to improvement of technology in other areas. The power circuit topology uses only four switches to provide five level modulation capability. Previously this could only be obtained with the use of eight switches requiring either two standard single phase bridges or the neutral point clamped, (NPC), configuration, [2-5]. Within the new topology greater utilisation of each switch is achieved by the use of a coupling transformer in each phase leg. The power circuit consists of four independent buck converters. This new topology is believed to be a new concept and is the subject of a patent application, [6]. The topology could be employed in three phase variable speed motor drives. By appropriate phase shifting of the modulation carriers the switch frequency component can be eliminated from the output spectrum, [7]. This could be of great importance in multi-megawatt drives where switching frequencies are normally less than 500Hz. Another very significant advantage of the new topology is that the shoot through fault which can occur in standard phase legs is eliminated. The coupling transformer together with the control system prevents any uncontrolled shoot through current from occurring. This will prove to be a very large benefit in the high power motor drive area.

In 1987 a 15kVA amplifier was developed for the same application by the University of Queenslands Physics Department, [1]. It was based upon a pulsewidth modulated bridge inverter supplied from a 560Vdc nominal bus. The inverter switching elements operated at a frequency of 20kHz. A uni-polar pulsewidth modulation scheme was adopted. This produces three distinct output levels and an effective output switching frequency of 40kHz. After extensive field testing this amplifier was shown to be deficient in several areas for the CSAMT application. The output current available proved inadequate in some situations. The need existed to increase the rating from 15kVA to 45kVA. Although the amplifier was capable of reproducing signals up to 10kHz the waveform quality and control performance was poor. Only low open loop gains are possible near 10kHz. At higher gains the 40 kHz output switching frequency ripple component caused erratic behavior of the modulator. An open loop bandwidth of 20kHz would be necessary to obtain adequate control loop performance at 10kHz.

To obtain the performance levels desired the second generation amplifier would require a substantial increase in the power frequency product over the original unit. Meanwhile, semiconductor technology has advanced considerably over the last five years. However, analysis showed that the increased performance of the semiconductor devices alone could not provide the required power frequency product. This lead to the development of a new inverter topology. This new topology allows a five level modulation strategy to be implemented, extending the maximum bandwidth and reducing the output peak to peak ripple current amplitude. The output ripple frequency becomes four times the device switching frequency.

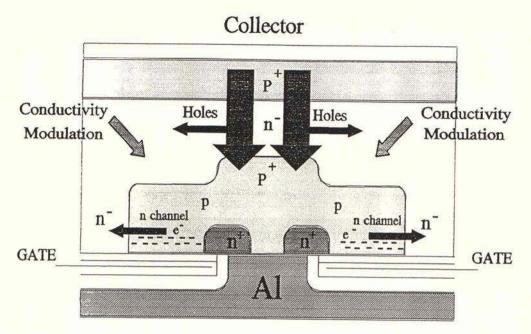

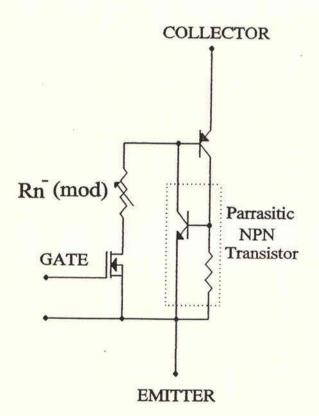

With the new topology a device switching frequency of 50kHz was required to obtain the necessary control bandwidth. The power devices used were 200A 1200V Insulated Gate Bipolar Transistors (IGBT's), [8]. These devices represent state of the art power switching semiconductor technology at the time of the project. However at a switch frequency of 50kHz, snubbing to reduce switching power loss, was a necessity.

The snubbing system chosen is an innovative combination of several published techniques, [9],[10-14]. Each buck converter has a self contained snubbing system. The design of this buck converter with snubbing system to obtain optimum overall results is a complex task, [15], requiring a number of iterative steps. Factors such as overall power loss, individual device power loss, device temperature rise, device maximum current/voltage stress and circuit complexity must all be considered. High power converters require considerable effort at the design stage.

Design errors in high power converters, unlike low power converters, are expensive to correct. Extensive use of the software package PSPICE, [16], was made to verify device current and voltage stresses prior to construction of the prototype. Very few problems were encountered in the full scale buck converter prototype.

The content of each chapter will now be described briefly.

Chapter Two of this report focuses on the new converter topology. It begins by reviewing conventional techniques used to construct switching amplifiers, [17],[1-2]. The suitability of each for this application is discussed. A detailed comparison of two, three and five level modulation schemes is presented. A TUTSIM simulation of a five level scheme was conducted to obtain the voltage and current output spectrum, [18]. The simulation shows that components at the switch frequency and two times the switch frequency can be eliminated. Spectral components are found to be centered around a 200kHz suppressed carrier at intervals of the modulation frequency for a 50kHz switch frequency. The operation of the new converter topology offering the capability of five level modulation is discussed in detail. Important converter design rules such as those relating to the coupling transformers are developed.

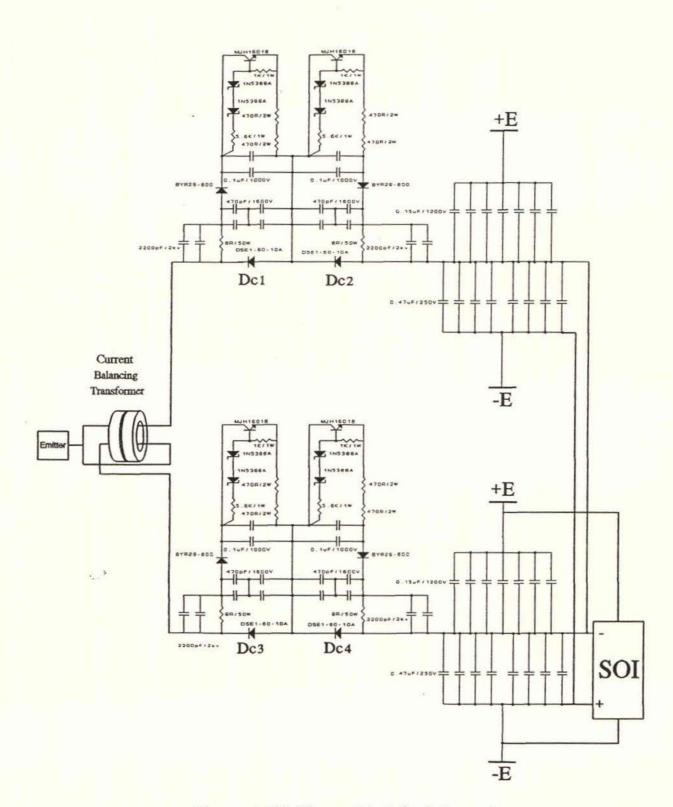

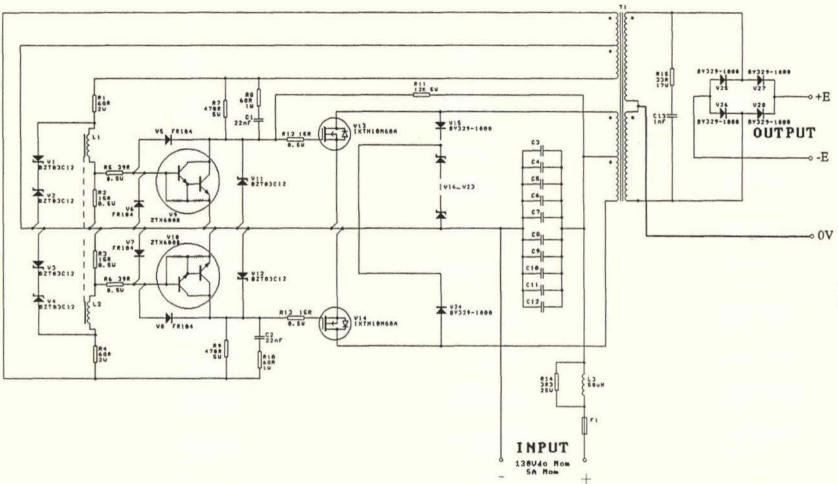

Because this converter is new, a new set of control strategies need to be developed. To maintain the five level modulation properly all buck converters must always remain in conduction. In addition to regulating the output current the controller must maintain conduction in all buck converters. Each buck converter consists of the main switching device and freewheel diode assembly plus associated snubbers. Because of the converter's high power rating and high operating frequency the snubbers are a significant system component. The buck converter employs both resonant reversing lossless snubbers and a voltage clamping system for the IGBT. The clamping system uses a pair of 500watt self oscillating inverters, (SOI's), to return energy to the dc supply. The choice of topology and operation of the Buck converters is thoroughly discussed and includes a set of typical system waveforms.

The third chapter presents a detailed study of the power semiconductors employed in the converter. A full understanding of the semiconductor device characteristics is fundamental to a good converter design. While it is possible to design and develop low power converters with little knowledge of semiconductor properties, this luxury can not be afforded at high powers and high switch frequencies. In large converters semiconductor performance dictates physical construction and layout. Therefore modifications due to unexpected variations in semiconductor performance are not easily accommodated in the prototyping stage. The key to a successful design is an accurate assessment of semiconductor performance in the design stage.

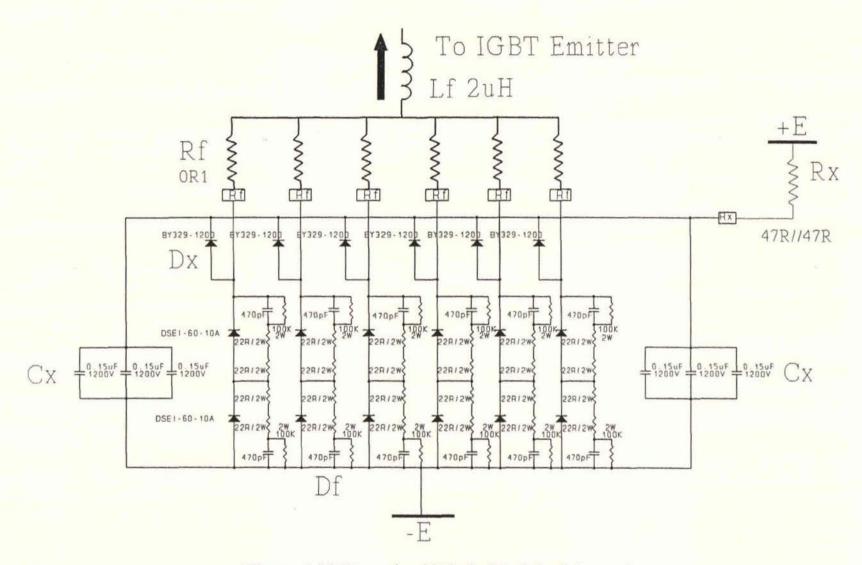

The converter uses a large number of high current high speed diodes. Because of the high switching frequency these diodes must have good reverse recovery characteristics. Where possible it was decided to standardise on one type of diode. After an extensive review of the latest manufacturers' data books the diode chosen was a 1000V 60A (DSE1-60-10A) device which was a new release by ABB-IXYS, [19-22]. The reverse recovery data indicated that this diode was significantly better than any similar rated device that was reviewed. However only data for one operating condition was available. The four major parameters that affect the reverse recovery performance are the forward current prior to commutation, the commutation dI/dt, junction temperature, and minority carrier life time. While the former three are essentially a function of the converter design the latter is a characteristic of the diode. In this case a reverse maximum current of 32A was specified for a forward current of 60A, commutation dI/dt of  $480A/\mu S$  and a junction temperature of 100°C. To be able to accurately design the converter it was necessary to know the reverse recovery current at significantly different operating conditions to those given.

Thus, it was considered essential that an accurate method of determining diode reverse recovery current be found. Review of the literature indicated that the most common method of approaching this problem was by formulation of models and subsequent simulation, [23-26]. While this yields good simulation results it is not a closed solution and thus inadequate for the design purpose. As part of this thesis relationships for the reverse maximum current are derived. The relationships are based on the charge control model of the P-N junction, [27-29]. Implicit equations that allow the calculation of the minority carrier lifetime from manufacturers data and then use this parameter to determine the reverse maximum current at other operating points have been developed. These equations are presented graphically and in lookup table form. When applied to diodes with comprehensive data a good match between predicted and actual characteristics has been found. The procedure though based on well known theory is presented in a unique and efficacious form for use in general power electronics design. The calculation of the minority carrier lifetime also allows an unbiased comparison of diode reverse recovery performance between devices from competing manufacturers. This new technique is believed to be a valuable tool to the power electronics designer, [30].

Another diode characteristic which is less widely documented but is of significant importance in large high frequency converters is transient forward recovery, [24,29,31]. In this case at high application rates of forward current the forward voltage exceeds its normal steady state level. In some cases the transient voltage may be greater than 50V. Because this overshoot voltage normally causes stress on other semiconductor devices it becomes an important design consideration. Section 3.3 is devoted to the discussion of the forward recovery process, its effect and estimation in various sections of the converter. The main switching device in the power circuit is a Toshiba MG200Q1US1 IGBT, [8]. Sections 3.5, 3.6 and 3.7 are devoted to a discussion of its characteristics, and method of calculation of its power loss.

Chapter Four gives a detailed description of the power circuit design, which is a long iterative task because of the complex interdependence of component values. Rather than presenting the full design process the selected values for the major components are presented and the choice in terms of worst case junction temperature, current stress or voltage stress is verified. The selection of each major component in each module is examined. Throughout the design extensive use is made of the results from Chapter Three with respect to diode reverse recovery. Two important components are the main snubber capacitor  $,C_s$ , and the dI/dt limiting inductor, Lf. These two components to a large extent govern the design of most of the remainder of the converter. Their selection is a complex task involving many variables with many iterative steps. In particular, the following factors must be considered: Main and auxiliary semiconductor device power loss, current stress and voltage stress; overall power loss and converter efficiency; IGBT minimum on and off times. Previous research has been found to focus primarily on optimisation of the overall IGBT switch and snubber efficiency., [15]. The choice of components a dictated by these other constraints is discussed in Chapter Four.

Chapter Four also describes the IGBT gate drive system. The design uses one gate drive module for each IGBT. These modules are electrically isolated from the control circuit. The control signals from the main control board are isolated by fiber optic links. Power is supplied at 100 kHz from a switch-mode power supply via transformers. This approach eliminates disturbance to the main controller due to coupled electrical interference from the power circuit. The design of well isolated, interference tolerant drivers is considered mandatory in high power, high frequency converters. The gate drive circuit also provides complete IGBT protection independent of the action of the main control system. The design philosophy adopted was to use all discrete circuitry operating at high current levels.

The design and operation of the clamping system SOI is also discussed. These SOI's use mosfets with a special driving circuit rather than the traditional bipolar transistor as the switching devices. The self oscillation is generated by the partial saturation of an auxiliary transformer, [12]. This results in greater efficiency in comparison with the more common approach of using main transformer saturation. At the close of Chapter Four the overall power loss is calculated at the rated output current of 100A with a 50% duty ratio with nominal bus voltage of 560V. This is used to calculate the cooling requirements.

A full rating prototype buck converter was constructed to verify the design. The test results from this converter are presented in section 4.8. The measured efficiency figures were found to contain a large tolerance because of the limited accuracy of the measurement equipment. In terms of component and heatsink temperature rises the performance of the converter was found to be adequate and in reasonable agreement with the design values.

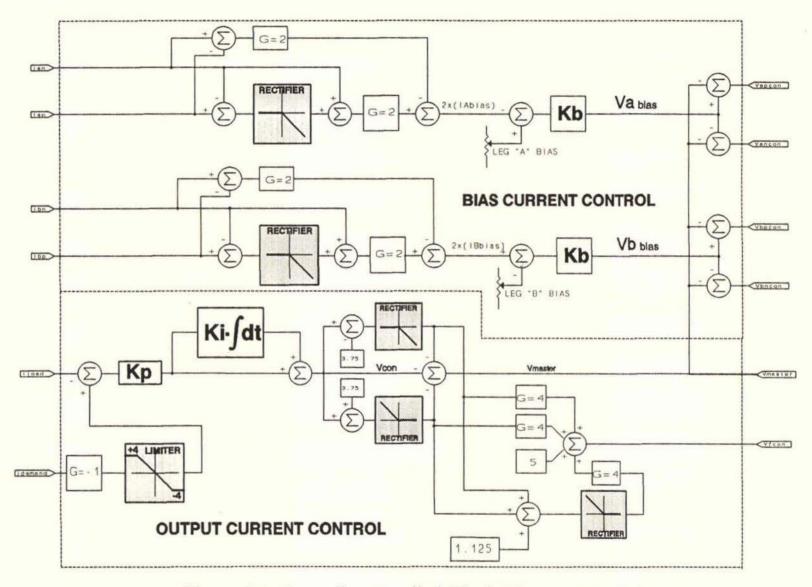

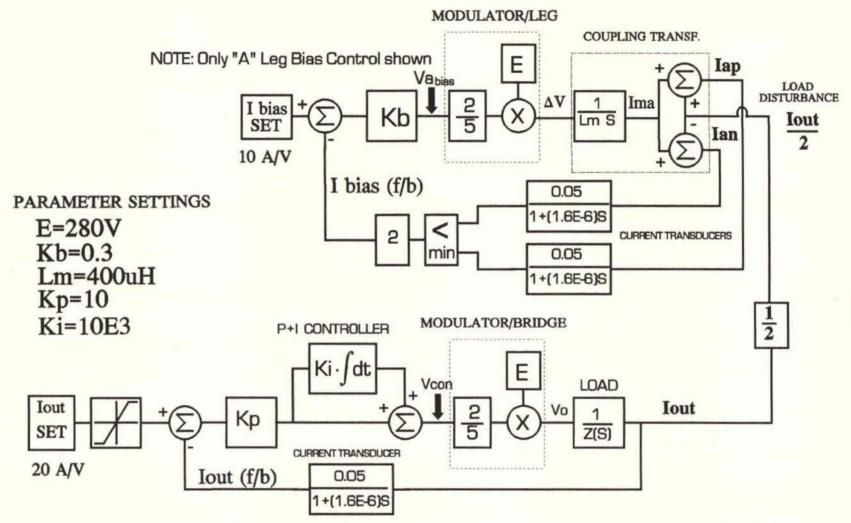

Chapter Five describes the control system operation and design. Because the converter topology is new, unique control strategies were developed. To obtain the five level PWM feature a four phase symmetrical ramp generator has been implemented. Each phase is responsible for generating the PWM signals for one buck converter. Multiple phase PWM has been applied in DC power supplies to reduce input and output ripple current, but does not appear to be well known to inverter designers, [32]. The techniques developed for this inverter could with some adaptation be applied to the neutral point clamped topology. Further research is being conducted into this technique. To maintain the five level modulation all buck converters must remain in conduction. This is equivalent to maintaining a bias current flowing down each leg. To achieve this the coupling transformer magnetising current must always be maintained above one half the output current.

A control loop which senses and regulates the bias current via manipulation of the coupling transformer magnetising current has been implemented. A second control loop senses and regulates the inverter output current. Due to the IGBT minimum on and off time constraints the inverter output voltage saturates at 75% of the bus voltage. This represents a severe restriction which traditionally has been a problem with high switching frequency converters. It has been overcome in this design by the use of a frequency dropping strategy. Once the minimum off or on time constraint is reached the control action is diverted to linearly reducing the frequency. The result is that the duty ratio, and hence the average output voltage, continues to increase. Using this technique the five level modulation properties are maintained. The resulting ripple current is kept low. The performance of this system has been found to be exceptionally good. It is believed that this innovative technique will be of significant benefit in variable speed motor drive systems.

The chapter develops the relevant design methods and analysis for the new control system. This includes derivation of equations which describe the interaction between control loops. Control loop performance verification was also carried out using the "MATLAB" mathematical analysis package, [33]. The results of the analysis are used to size system components and set parameters.

Detailed simulation of the combined controller and power circuit was carried out using the dynamic systems analysis package "TUTSIM", [18]. The model was constructed so that on a functional level it would resemble closely the hardware design. The purpose was twofold, first it was used to verify the predicted performance, secondly because of the model's detail it was effectively a pre-hardware prototype. Using this procedure labor intensive hardware redesign is avoided. In a large converter it is not practical nor advisable to debug the control system using the full scale power circuit.

A tenth scale model of the power circuit was designed and constructed for the purposes of debugging and tuning the control system. The controller sends and receives signals identical to those in the full scale unit. Chapter Six is devoted to the presentation of results of the "TUTSIM" simulation and the tenth scale model. The very good agreement of the two serves to illustrate the power of systems level simulation. The use of dynamic systems packages for simulation of power electronic systems appears to be under exploited. Using the ideas developed as a part of this project there is great potential for further work in this area. The scale model and simulation results verify the predicted operational characteristics. The output waveform quality up to a modulating frequency of 1kHz is exceptionally good with the total harmonic distortion being less than 0.35%. Performance between 1 and 10 kHz deteriorates with increasing frequency but is still more than adequate for the application.

At this time the full scale amplifier power circuit is not complete. However few difficulties are expected during the commissioning stage because of the methodical design and subsequent verification procedures that have been followed.

### 2. CONVERTER TOPOLOGY

This chapter focuses on the new five level converter topology. It begins with a review of known techniques which have been used to construct switching amplifiers. These include the Cuk converter, standard bridge inverter, neutral point clamped inverter and multiple bridge inverter configurations. The suitability of these approaches in relation to the CSAMT application is discussed. In terms of extending bandwidth and improvement of waveform quality multilevel PWM schemes are of benefit in switching amplifier applications. A detailed comparison of two, three and five level schemes is presented. The five level modulation system is simulated with the results being presented. The new five level converter topology uses four switches compared with traditional inverter configurations which require eight. Better switch utilisation is obtained by the use of four buck converters linked by two coupling transformers. The operation and important design parameters of the new topology are discussed.

The buck converter snubbing system topology and operation are also described. The main switch snubbing system is a resonant reversing lossless configuration combined with an active clamp. The snubbing system design equations together with typical buck converter waveforms are presented.

#### 2.1 Conventional Converter Topologies

The choice of the switching converter topology is a critical part of the overall amplifier design. If state of the art semiconductor technology is used then the topology will determine the equipment performance limitations. Since the performance requirements are particularly demanding for this design the topology selection is very important. The following topologies have been previously used for four quadrant wide bandwidth switching amplifiers:

- (a) Cuk Converter, [17]

- (b) Bridge Converter, [1]

- (c) Multi level modified Bridge Converters, [2]

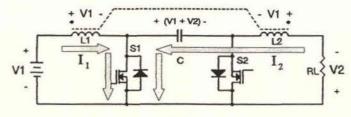

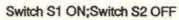

The two quadrant Cuk converter is illustrated in Figure 2.1. The Cuk converter which is a reasonably new development in converter topologies has some important advantages over conventional Buck and Boost converters. The most significant property which makes it very useful for switching amplifiers is its property of having zero output ripple current, provided coupled inductors (L1 and L2) are used. This gives the possibility of wide control bandwidths and therefore excellent performance. A 40 watt amplifier using this topology has been documented, [17]. This amplifier gave very good performance with a flat frequency response to 20kHz and a Total Harmonic Distortion of 0.1%. However this converter has some serious short comings when a design is attempted at the power levels required in this unit. To aid in the appreciation of this, a brief discussion of the converter operation is included.

Under steady state operating conditions the coupling capacitor, C, has an average voltage of  $(V_1 + V_2)$  across it. The capacitor is normally sized such that the ripple voltage over it is relatively small and can be neglected. This condition is forced on the designer in order to keep the capacitor dielectric losses low as well as to keep the output ripple current low. When S<sub>1</sub> is turned on (S<sub>2</sub> off) V<sub>1</sub> is applied across L<sub>1</sub> and current I<sub>2</sub> flows through S<sub>1</sub>. The current I<sub>2</sub> flows through L<sub>2</sub> and C also via S<sub>1</sub>. Notice that the voltage V<sub>1</sub> is also applied across L<sub>2</sub>, this is the reason why the two windings can be coupled. While S<sub>2</sub> is on (S<sub>1</sub> is off) the voltage V<sub>2</sub> is applied across L<sub>2</sub> and L<sub>1</sub>. The current I<sub>1</sub> flows through L<sub>1</sub> and C via S<sub>2</sub>. The current I<sub>2</sub> flows through L<sub>2</sub> also via S<sub>2</sub>. During the entire cycle energy is transferred between the source and the load via the capacitor and there is an interchange of energy between the capacitor and the magnetic core.

Switch S1 OFF;Switch S2 ON

Figure 2.1 Cuk Converter Operation

By consideration of charge conservation in the capacitor and input to output power equality the D.C. transfer ratio can be easily shown to be:

$$V_2 = V_1 \frac{D}{1 - D}$$

2.1-1

$$D = \frac{T_1}{T_1 + T_2}$$

2.1-2

The variables  $T_1$  and  $T_2$  are the on times for  $S_1$  an  $S_2$  respectivly.

An important property of the coupled inductor configuration is that if the turns ratio  $\sqrt{\frac{L_1}{L_2}}$  is adjusted to be equal to the coupling factor then the effective output inductance can be shown to approach infinity. This means that in the ideal case the output ripple can be forced to zero. This is an excellent property which makes this converter ideal for switching amplifier applications. However the coupling capacitor at high power levels is of considerable physical size since it is effectively transferring the entire converter load and must be rated at least two times the input voltage. In addition to this the two switching devices must be capable of handling twice the rated load current at twice the input voltage making any design difficult at higher power levels. The switch snubbing requirements are as a result considerable.

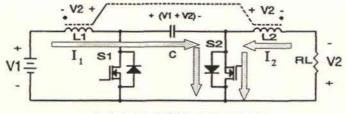

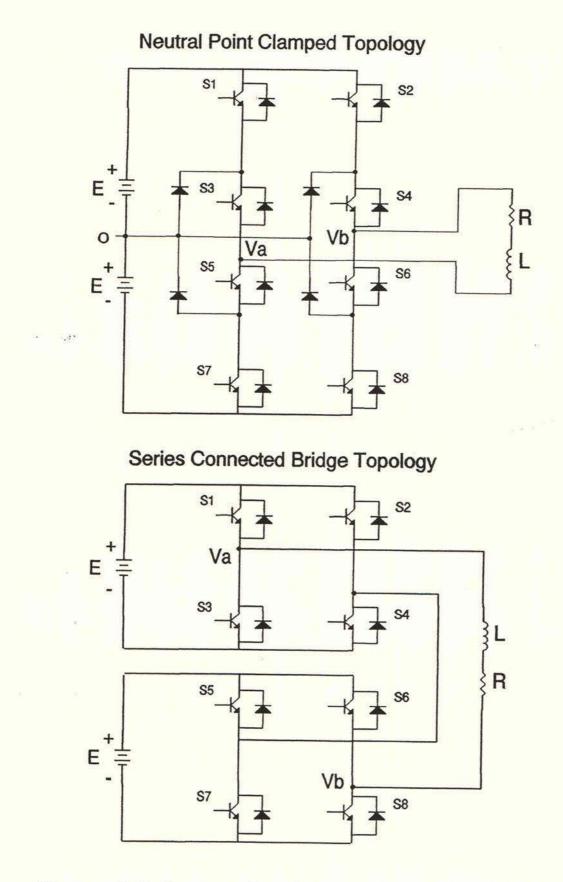

Although the topology has some very good advantages it is not a practical solution at high powers. A more practical four quadrant topology is the standard bridge inverter as shown in Figure 2.2. The simplest switching strategy for the bridge inverter is to alternately switch diagonal pairs of switches. For a bus voltage of 2E there are two possible output levels, 2E and -2E. This gives rise to two level pulse width modulation as illustrated. The output frequency in this case is the same as the switch frequency. Phase shifted leg switching can also be used to obtain double the output ripple frequency.

Figure 2.2 Bridge Inverter Modulation Techniques

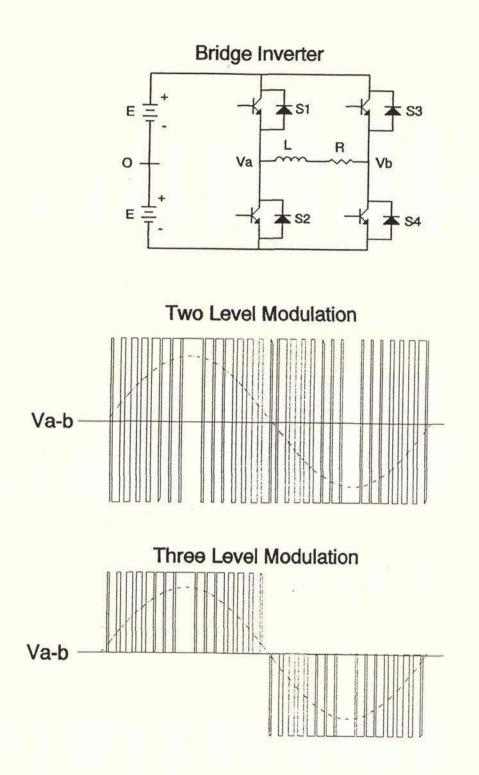

This also results in the production of three output levels, +2E, 0, -2E. The same technique was used in the earlier amplifier design, [1]. Because the effective frequency is doubled and the voltage step is halved the maximum ripple current in the output inductor is one quarter that of the two level case. This gives a significant advantage for a little extra complexity in the control system. A further extension of this is five level modulation which results in an output frequency of four times the switch frequency and a voltage step of one quarter that of the two level case. The result of this is a sixteen fold reduction in the maximum ripple current. This is a large advantage which has been exploited in a number of high power converters. In particular Marchesoni, [2], has applied the technique in amplifiers with a rating of 3.6 MVA and a bandwidth of 10kHz for application in nuclear fusion experiments. It is quite clear then that this technique would yield acceptable results in the case of this amplifier. The two extra switching levels are normally obtained by the addition of two phase legs in either the neutral point clamped configuration or the series connected bridge configuration as illustrated in Figure 2.3. A typical sine wave modulated five level waveform is shown in Figure 2.4. Marchesoni has proposed a quite complex control system to obtain the correct switch sequence to give the five levels. However it was believed that a simple phase shifting strategy was all that was required, this was later confirmed by simulation and a scale model.

#### 2.2 Multilevel Modulation

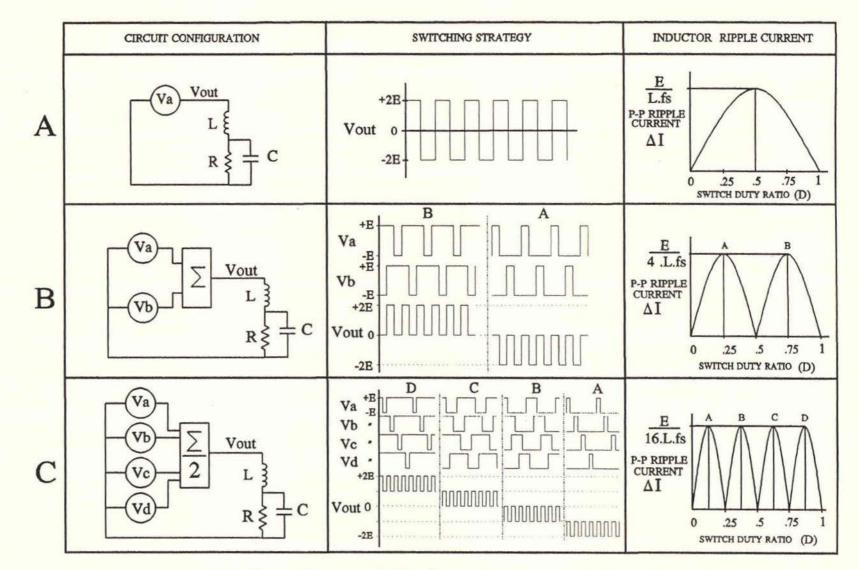

The benefits of multilevel switching using phase displaced legs is illustrated in Figure 2.5. Part(a) shows a two level inverter supplied at 2E. This can be modeled as one source  $V_a(t)$  which switches between +2E and -2E. Part (b) shows a three level inverter which can be modeled by two sources which switch 180° out of phase and are added to produce the output voltage. Each source represents one inverter leg. Three output levels are produced and the output frequency is twice the switch frequency. A five level inverter model is shown in Part (c).

# Figure 2.3 Conventional Five Level Topologies

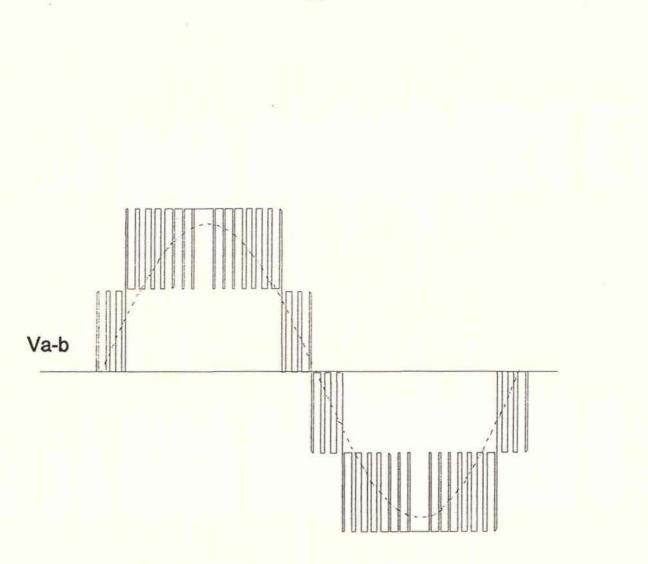

Figure 2.4 Five Level Modulation Waveform

Figure 2.5 Two, Three and Five Level Switching Strategy Comparison

Two more sources are introduced, with all sources being phase displaced by  $90^{\circ}$ . The addition of the four sources produces the five possible levels as illustrated. In each case each level is produced in a different duty cycle range. The output inductor ripple current as a function of the duty ratio is also shown for each case. For the two level inverter the maximum occurs at a duty ratio of one half and has a value of:

$$\Delta \mathbf{I} = \frac{\mathbf{E}}{\mathbf{L} \quad \mathbf{f}_{\mathbf{s}}} \tag{2.2-1}$$

For the three level inverter the maximum ripple occurs at one quarter and three quarters duty ratio and has a value of:

$$\Delta I = \frac{E}{4 L f_s}$$

2.2-2

For the five level inverter maximums occur at duty ratios of one eighth, three eighths, five eighth an seven eighths with a value of:

$$\Delta I = \frac{E}{16L f_8}$$

2.2–3

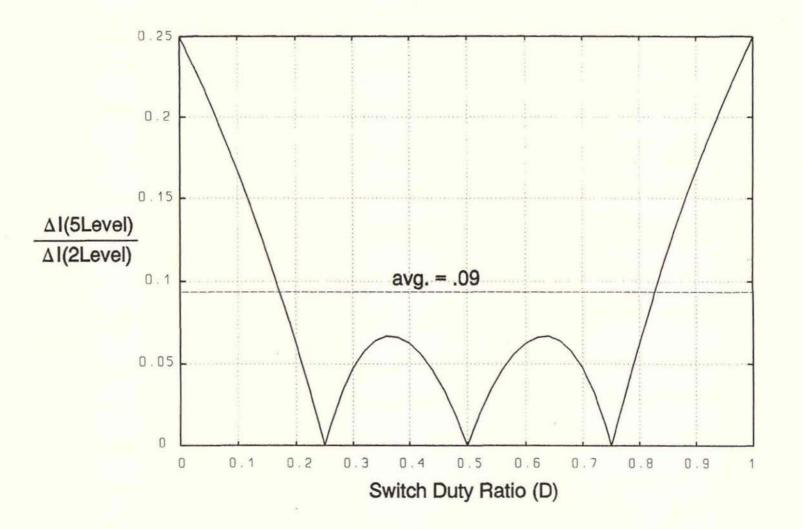

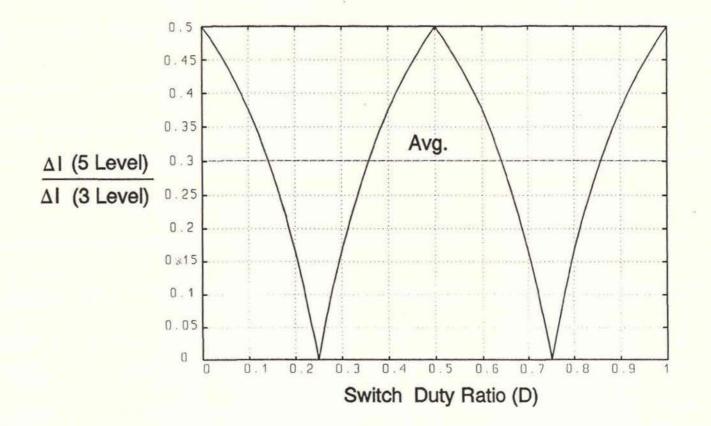

Figure 2.6 gives a better appreciation of the overall improvement in output current ripple of five level modulation over two level modulation as a function of duty ratio. The average ratio of the peak to peak ripple for a five level system to a two level system is 0.09. This means that a five level system switching at 50kHz is, in terms of peak ripple current, as good as a two level system switching at 556kHz. This represents a substantial improvement in output quality and the achievable control bandwidth. The improvement of a five level modulation system over a three level system is also displayed in Figure 2.7. In this case the average improvement is one third. A five level modulation simulation was run using "TUTSIM",[18], to determine the output voltage and current spectrum for a 10kHz input signal.

Figure 2.6 Current Ripple Improvement of 5 Level Over 2 Level Modulation as a Function of Duty Ratio

Figure 2.7 Current Ripple Improvement of 5 Level Over 3 Level Modulation as a Function of Duty Ratio

The Tutsim model is shown in Figure 2.8. A common 50kHz symmetrical ramp signal is delayed by  $5\mu S_{,10\mu}S$  and  $15\mu S$  to obtain the four phase set. Each ramp is compared with the modulating signal to produce the four phase PWM. These are applied to relays which switch between +E and -E (+/-280 volts in this case). These are summed to produce the five level load voltage. The load has been set to  $2\Omega$  resistance in series with  $200\mu$ H inductance. The simulated load voltage and current for a 10kHz modulating signal is shown in Figure 2.9. The voltage spectrum shown in Figure 2.10 is of interest since it shows that the spectral components are side bands spaced at increments of the modulating frequency around a suppressed carrier at the switch frequency multiplied by four. In this case the first side band is at  $200 \pm 10$  kHz. Note that there is no component at the switch frequency of 50 kHz. Perfect cancellation is to be expected since this is an ideal simulation, however in a real system perfect cancellation cannot be obtained. Nevertheless the 50kHz component can be kept relatively low by careful design. The current spectrum is shown in Figure 2.11. The high frequency spectral components produced by the five level scheme are found to be heavily attenuated by the load with the highest being at 150kHz with an amplitude of only a fraction of an amp. for a 30Arms output. The control bandwidth is normally limited by the peak to peak ripple current. The converter plus controller is normally considered to be a linear system in so far as the control analysis is concerned. This assumption however breaks down once the ripple level at the input to the pulse width modulators becomes excessive. Normally bandwidths are restricted to one tenth of the effective switching frequency. This would mean a bandwidth of 20kHz should be easily obtained with a five level converter switching at 50kHz. This topic will be more thoroughly explored in Chapter Five.

Figure 2.8 Five Level Modulation Simulation "TUTSIM" Model

24

.

.

Figure 2.9 Five Level Modulation Simulation Results (Load Voltage and Current)

25

Figure 2.11 Five Level Modulation Simulation Load Current Spectrum

27

## 2.3 The New Five Level Converter Topology

As previously indicated five level modulation has normally been achieved by the neutral point clamped or the series connected bridge topology. In both cases two extra phase legs and hence four switches are added to produce the two extra levels. For the application this represented an unacceptable increase in the power circuit complexity and so a different approach was needed. An alternative solution is to replace the bridge converter by four buck converters. If the buck converters operate in the continuous conduction mode they produce a two level output waveform. These can be controlled to produce the four phase waveforms as shown in part(c) of Figure 2.5. A five level modulation scheme can therefore be achieved if the outputs of the four buck converters can be combined. Figure 2.12 shows how the combining was achieved. The two buck converters from one phase leg are coupled by a center tapped auto transformer and the load is connected between phase legs. The phase leg output voltages will be given by:

$$V_{a}(t) = \frac{v_{ap}(t) + v_{an}(t)}{2}$$

2.3-1

$$V_{b}(t) = \frac{v_{bp}(t) + v_{bn}(t)}{2}$$

2.3-2

The buck converter voltages all have identical pulsewidth modulated waveshapes but are phase displaced. With  $V_{ap}(t)$  as a reference and a buck converter switching period of T, the following equations can be written:

$$V_{an}(t) = V_{ap}(t-T/4)$$

2.3-3

$$V_{bn}(t) = -V_{ap}(t-T/2)$$

2.3-4

$$V_{bp}(t) = -V_{ap}(t-3T/4)$$

2.3-5

And the output voltage is:

$$V_{out}(t) = V_a(t) - V_b(t)$$

2.3-6

Figure 2.12 New Five Level Inverter Topology

Therefore combining equations:

$$V_{out}(t) = \frac{V_{ap}(t) + V_{ap}(t - T/4)(V_{ap} - T/2) + V_{ap}(t - 3T/4)}{2}$$

2.3-7

The output will therefore be five level providing all the buck converters remain in conduction. Because the positive buck converters "AP" and "BP" can only source current and the negative buck converters "AN" and "BN" can only sink current a bias current must be maintained flowing down each leg at all times so that all converters remain in conduction. This bias current can be created by forcing a volt-second difference between the top and the bottom converters which causes a magnetizing current  $I_{ma}$  to be established in  $L_m$ . The discussion of the bias current will be limited to that concerning the "A" leg, the operation of the "B" leg being identical. This volt-second difference is easily produced by forcing a deviation in pulsewidths at the modulator stage of the controller. The bias current is given by the following: (note: all the following equations refer to average currents)

$$I_{\text{bias}} = \frac{I_{\text{ap}}(t) + I_{\text{an}}(t) - \text{abs}[I_{\text{ap}}(t) - I_{\text{an}}(t)]}{2}$$

2.3-8

The above expression is simply the minimum out of  $I_{ap}$  and  $I_{an}$ . The two converter currents from Figure 2.12 are related to the leg magnetizing current  $I_{ma}$  and the output current  $I_o$  by the following relationships:

$$I_{ap}(t) = I_{ma}(t) + \frac{I_0(t)}{2}$$

$$I_{an}(t) = I_{ma}(t) - \frac{I_0(t)}{2}$$

2.3-9

2.3-10

Therefore from equation 2.3-8:

$$I_{bias}(t) = I_{ma}(t) - \frac{abs[I_0(t)]}{2}$$

2.3-11

And  $I_{ma}$  can be controlled by the differential volt seconds across  $L_m$  with the following relationship applying:

$$I_{ma}(t) = \frac{1}{L_m} \int \Delta V(t) dt \qquad 2.3-12$$

A simple proportional negative feedback control loop can be used to set the bias current to a desired level. However it can be seen from equation 2.3-11 that the output current acts as a disturbing influence in this loop and so it is found that it is not practical nor desirable to design a controller which can hold the bias current constant, this is discussed in more detail in Chapter Five.

An incidental but very significant benefit of this topology is the elimination of the "leg shoot through fault" possibility of the normal bridge inverter. In high voltage systems this can cause the complete destruction of the inverter components. For this inverter the through current(bias current) is a controlled variable.

#### 2.4 Coupling Transformer Selection

The selection of the coupling transformer is effected by the following factors:

- (a) Buck converter maximum peak to peak ripple current

- (b) Performance of the bias current control loop

The performance of the bias current control loop is the most complex factor to analyse. During dynamic changes in output current the bias current control loop will act to keep the bias current constant as already explained. In doing this it can be shown that a 50kHz spectral component will be introduced into the output voltage. To show that this is true consider that the output current is increasing at a fixed rate, m, so that:

$$I_0 = mt$$

2.4–5

Now it will be assumed that the control loop has the ability to maintain the bias current constant at I<sub>set</sub>. This means that:

$$I_{\rm m} = I_{\rm set} + \frac{\rm m}{2} t \qquad 2.4-2$$

To obtain  $I_m$  a voltage  $\Delta V$  must be impressed across  $L_m$  which will be given by:

$$\Delta V = L_m \frac{dI_m}{dt} = L_m \frac{m}{2}$$

2.4-3

This means a constant differential voltage must be maintained across  $L_m$  to keep  $I_{bias}$  constant when the output current is rising at a constant rate. Because the phase rotation of the converter must be ap;an;bn;bp to obtain the five level output the converters contribute one pulse in the same order to the output each 20uS as illustrated in Figure 2.13. To create the differential voltage between the "AP" and "AN" converters the "AP" pulse will be wider than the "AN" pulse and likewise the "BP" pulse will be wider than the "BN" pulse. Because of the phase rotation the result is two long pulses followed by two short pulses. This pattern repeats itself every  $20\mu$ S and therefore has a 50kHz fundamental component. The difference between the two waveforms clearly illustrates this. The 50kHz component can be shown to be proportional to  $L_m$  and m. This 50kHz component is undesirable since it degrades the output waveshape as well as giving potential problems in the main current control loop. The exact calculation of the 50 kHz component requires complex analysis beyond the scope of this project.

Figure 2.13 The Effect of Bias Current Control on the Modulation Integrity

The approach in this design has been to not make the bias current control loop respond to fast rates of change in output. That is its bandwidth is limited which avoids the problem described above. However this results in the necessity of setting the bias current slightly higher. This leaves the buck converter peak to peak ripple current as the major factor involved in the selection of Lm. The low power model was constructed with  $L_m = 400 \mu H$ . The "TUTSIM" simulation and the low power model both gave quite acceptable results using this value. The simulation showed that  $L_m$  could be reduced to 200µH before the performance degraded. It was found by simulation that for inductances below  $200\mu$ H the whole system became prone to chaotic modes of behavior. With only a small magnetizing inductance small switching descrepencies can cause large changes in the output current. This can lead to complex non-linear interactions between the two control loops which is thought to lead to the disturbances that occurred. Although it was intended to make  $L_m = 400 \mu H$  and all the low power and simulation testing was based on this value, because of the restrictions of core sizes and availability the actual implemented value will be  $325\mu$ H. This is constructed from six SIEMENS UU 93/152/30; Seferrit N27 cores with a 7.5mm gap between cores. The winding consists of 28 turns of 25mm<sup>2</sup> litz conductor with a center tap.

The peak to peak ripple current in  $L_m$ , which is also that carried by the converters since the output ripple is considered negligible, can be found by realising that the maximum time for which the bus voltage is applied across it is  $5\mu$ S. The ripple current will therefore be given by:

$$\Delta I = \frac{2E \ \Delta t}{L_{m}}$$

$$= \frac{2 \times 336 \times 5}{325} = 10.3 \text{ A p-p}$$

2.4-4

This ripple is added to the bias current in addition to the output peak current. This effects how low the bias current can be set. In this respect a peak current of 5.15 A represents an acceptable amount.

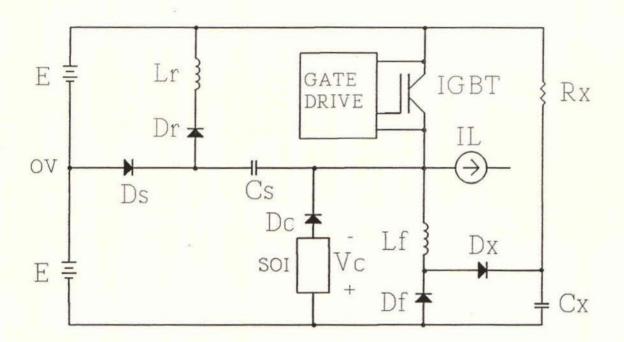

## 2.5 Buck Converter Cell Topology

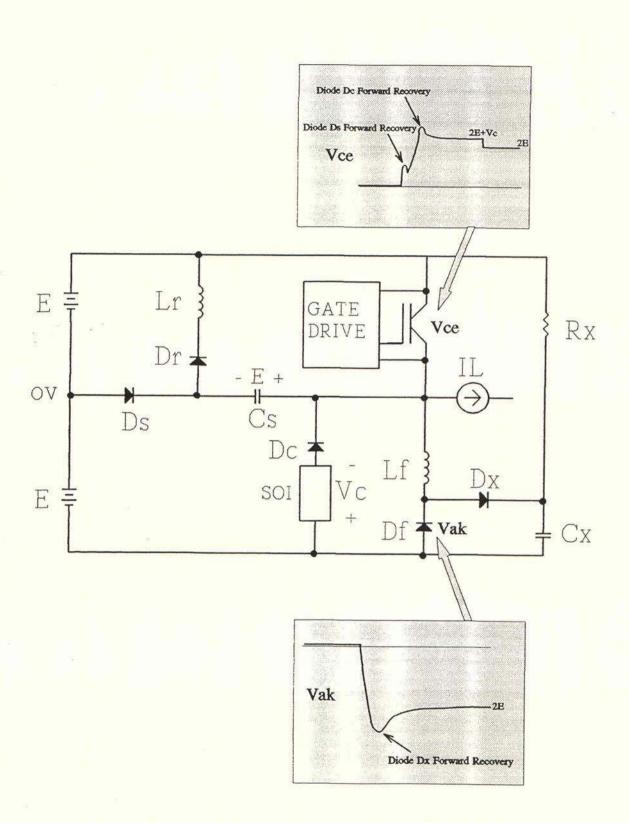

A simplified schematic of the chosen Buck converter cell is shown in Figure 2.14. The primary factor involved in the selection of the Buck converter cell topology is the necessity to keep the switching losses in the IGBT and freewheel diodes to an acceptable level. To reduce the switching loss snubbers are employed. There is a preference in high power converters for lossless snubbing systems to be implemented. The extra complexity of lossless snubbing is justified since the lost power would otherwise be so high that it becomes difficult to dissipate with an acceptable temperature rise. There have been many lossless snubbing systems proposed in the literature, [10-14]. The basic principle is always to reduce the IGBT switch on and switch off loss as well as the freewheel diode reverse recovery loss. The reverse recovery loss is controlled by the peak reverse current. This is reduced by limiting the current diversion, (di/dt), rate from the freewheel diodes  $(D_f)$  to the IGBT. Because of the addition of Lf the IGBT turn on loss is also kept low since the rate of rise of collector current is slow relative to the devices inherent rise time. Limitation of di/dt is achieved by the addition of the inductor  $L_f$  in series  $D_f$ . This diode reverse recovery current also adds to the peak current which the IGBT is required to carry. From this point of view it is also desirable that it be reduced. However the inclusion of  $L_f$  means that the IGBT turn off the load current can only be transferred to the freewheel diodes at a limited rate. This rate is determined by how high an IGBT collector emitter voltage overshoot can be tolerated at turn off.

The IGBT turn off loss is limited by providing an alternate path for the load current with a controlled rate of increase of collector emitter voltage to a peak level which is well within the devices capability. A capacitor is normally used to control the rate of rise of collector emitter voltage. If this capacitor is made sufficiently large it can also be made to completely divert the load current into  $L_f$  without  $V_{ce}$  becoming excessive. This however results in a relatively long diversion time and large snubber capacitors which makes this approach impractical for high operating frequencies.

Figure 2.14 Simplified Positive Buck Converter Cell

A better approach is to utilise the capacitor to just limit the rate of rise of voltage such that the turn off energy is at an acceptable level and use a lossless clamp to limit the maximum collector emitter voltage.

The lossless snubbing/clamping system finally chosen is a combination of two techniques as shown in Figure 2.14. A resonant resetting capacitive dv/dt IGBT snubber was implmented which requires access to a d.c. supply center point, which is normal for high voltage buses. This topology was the least complex out of those reviewed, [11]. The lossless clamping system uses a self oscillating inverter (SOI) to feed the energy associated with the magnetization of L<sub>f</sub> back to the supply, [13]. The clamp voltage V<sub>c</sub> controls the IGBT overshoot and hence the current diversion rate. The clamp system D<sub>c</sub> and V<sub>c</sub> guarantees that the IGBT collector emitter voltage is restrained. The SOI is tied to the supply bus, this means the clamp voltage is determined by the bus voltage and the clamp energy associated with the magnetization of L<sub>f</sub> is conserved. It is possible to use only the clamp and omit the the snubber but the switching loss will be considerable. To illustrate this point the loss will be calculated. Energy would be dissipated during the IGBT current fall time of 200nS. For E = 336V, a clamp voltage of 156V and a load current of 100A the power dissipation for a switch frequency of 50kHz would be:

$$P_{s} = (2E + V_{c}) \frac{I_{L}}{2} t_{f} f_{s}$$

2.5-1

$$= 828 \times \frac{100}{2} \times 0.2 \times 0.05 = 414$$

watts

As will be shown in Chapter Four this is considerably more than the conduction loss (178 watts worst case) and is unacceptably high.

A better approach is to utilise the capacitor to just limit the rate of rise of voltage such that the turn off energy is at an acceptable level and use a lossless clamp to limit the maximum collector emitter voltage.

The lossless snubbing/clamping system finally chosen is a combination of two techniques as shown in Figure 2.14. A resonant resetting capacitive dv/dt IGBT snubber was implmented which requires access to a d.c. supply center point, which is normal for high voltage buses. This topology was the least complex out of those reviewed, [11]. The lossless clamping system uses a self oscillating inverter (SOI) to feed the energy associated with the magnetization of L<sub>f</sub> back to the supply, [13]. The clamp voltage V<sub>c</sub> controls the IGBT overshoot and hence the current diversion rate. The clamp system D<sub>c</sub> and V<sub>c</sub> guarantees that the IGBT collector emitter voltage is restrained. The SOI is tied to the supply bus, this means the clamp voltage is determined by the bus voltage and the clamp energy associated with the magnetization of L<sub>f</sub> is conserved. It is possible to use only the clamp and omit the the snubber but the switching loss will be considerable. To illustrate this point the loss will be calculated. Energy would be dissipated during the IGBT current fall time of 200nS. For E = 336V, a clamp voltage of 156V and a load current of 100A the power dissipation for a switch frequency of 50kHz would be:

$$P_{s} = (2E + V_{c}) \frac{I_{L}}{2} t_{f} f_{s}$$

2.5-1

$$= 828 \times \frac{100}{2} \times 0.2 \times 0.05 = 414$$

watts

As will be shown in Chapter Four this is considerably more than the conduction loss (178 watts worst case) and is unacceptably high.

The unclamped peak voltage is:

$$V_{p} = 2E + I_{L} \sqrt{\frac{L_{f}}{C_{s}}}$$

2.5-2

The cosine decay time is:

$$t_3 - t_2 = \frac{\pi}{2} \sqrt{\frac{1}{L_f C_s}}$$

2.5-3

The case where the voltage reaches its peak only occurs at low load currents. It is assumed in Figure 2.15 that the load current is high and the clamp voltage is reached with the current in  $D_s$  being diverted to to the clamp. This current then decays linearly over  $t_3$  to  $t_4$ . The diode  $D_f$  takes up current over this period due to the clamp voltage diverting current to  $L_f$ . The diversion to  $L_f$  is lossless with energy being stored in  $C_s$  and also transferred back to the supply via the active clamp. At the IGBT turn-on two processes occur. The first process is the diversion of the load current from  $D_f$  to the IGBT at a rate determined by:

$$\frac{\mathrm{dI}_{\mathrm{f}}(\mathrm{t})}{\mathrm{dt}} = \frac{2\mathrm{E}}{\mathrm{L}_{\mathrm{f}}}$$

2.5-4

The value of  $L_f$  is selected to limit the reverse recovery loss in  $D_f$ . At  $t_6$  diode  $D_f$  recovers. The IGBT turn on loss is low as its collector voltage falls before any significant collector is established. The second process is the resonant resetting of capacitor  $C_s$ . At  $t_5$  a resonant current begins to flow in  $L_r$ ,  $D_r$ ,  $C_s$  and the IGBT. The current is:

$$I_{r}(t) = (V_{c} - E) \left[ \frac{C_{s}}{L_{r}} \sin \frac{t}{\sqrt{C_{s}L_{r}}} \right]$$

2.5-5

Figure 2.15 Positve Buck Converter Cell Waveforms

This current persists until  $C_s$  is reset to E. Current then transfers to  $D_s, D_r$  and  $L_r$ . The inductor decays linearly to zero at the following rate:

$$\frac{\mathrm{dI}_{\mathrm{r}}(\mathrm{t})}{\mathrm{dt}} = \frac{\mathrm{E}}{\mathrm{L}_{\mathrm{r}}}$$

2.5-6

During this period the capacitor overcharge energy due to the clamping action during the IGBT turn-off is returned to the supply.

# **3. POWER DEVICE MODELING**

An important part of any high power converter design is the determination of the power device voltage stress, current stress and power dissipation. These are used in an iterative process to:

- (a) select the power devices

- (b) determine suitable snubbing

- (c) determine the cooling requirement

The development of accurate device models is fundamental to calculation of the power semiconductor stress levels. In this chapter the modeling of the power diodes and the IGBT will be considered.

The selected diodes had reverse recovery data limited to one operating point. This necessitated the development of a procedure for the calculation of the reverse recovery performance from limited data. A large proportion of the chapter is devoted to semiconductor diode charge control theory and the subsequent development of this procedure. Because the SPICE circuit simulation package has been used for design verification its diode reverse recovery modelling technique is examined in detail, [44].

Another diode characteristic which is of importance is forward recovery. The mechanism of forward recovery and its implications in this converter are also discussed.

### 3.1 Power Diode Physics

Before the modeling is discussed the physics of the semiconductor diode will be reviewed.

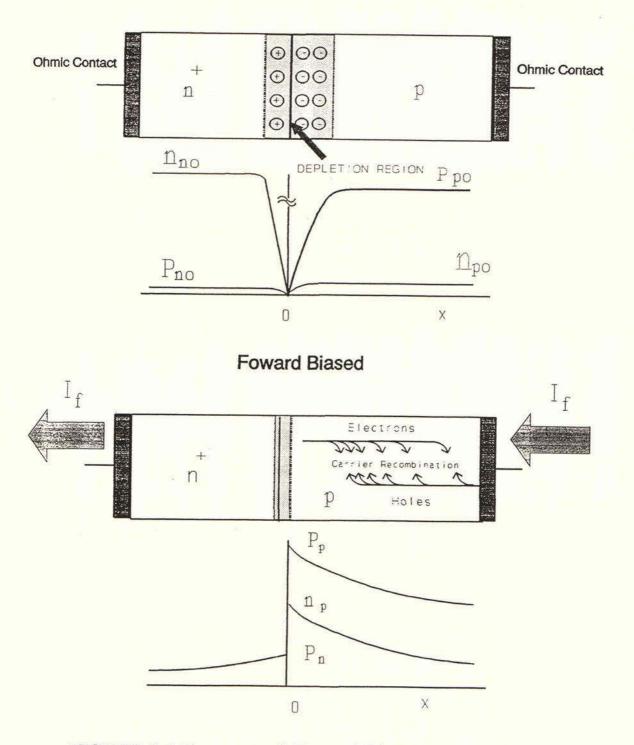

Figure 3-1 shows important features of a  $n^+$ - p junction diode in the reverse and forward biased conditions. The following symbols are used:

$n_{no}-n^+$  region equilibrium electron(majority carrier)concentration  $n_n - n^+$  region electron (majority carrier) concentration  $p_{no}-n^+$  region equilibrium hole (minority carrier) concentration  $p_n - n^+$  region hole (minority carrier) concentration  $p_{po}-p$  region equilibrium hole (majority carrier) concentration  $p_p - p$  region hole (majority carrier) concentration  $n_{po}-p$  region equilibrium electron(minority carrier)concentration  $n_{p}-p$  region equilibrium electron(minority carrier)concentration

The  $n^+$  region is heavily doped as compared with the p region as displayed by the reverse biased charge concentration diagrams, in practice  $n_{no}$  can be two or three orders of magnitude greater than  $p_{po}$ . The charge concentration is presented on a logarithmic scale. Under zero bias conditions because of the charge concentration gradients holes will diffuse from the p region to the  $n^+$  region and electrons will diffuse from the p region. The diffusion current density is directly proportional to the charge concentration gradient with respect to distance, x.

$$\begin{aligned} J_{\text{diff}} &= q D_{\text{p}} \frac{d \text{p}}{d x} + q D_{\text{n}} \frac{d n}{d x} & 3.1-1 \\ J_{\text{diff}} &- \text{Total diffusion current density} \\ q &- \text{Electronic charge} \\ D_{\text{p}}, D_{\text{n}} - \text{Diffusion coefficients} \\ p, n &- \text{Charge concentrations} \end{aligned}$$

**Reverse Biased**

In both cases these diffusing carriers will combine with majority carriers in the opposite region. The result is a depletion of mobile carriers in the junction area the junction area resulting in an electric field between the remaining accepter atoms in the p region and donor atoms in the  $n^+$  region. This electric field causes a drift of charges in an opposing direction to the diffusion movement.

$$J_{\rm drift} = q \left(\mu_{\rm p} p + \mu_{\rm n} n\right) E \qquad 3.1-2$$

$J_{drift}$  – Drift current density E – Electric field strength  $\mu_p, \mu_n$  – Carrier mobility constants

A balance is reached between the drift flow (current) and the diffusion flow (current) and no net charge movement occurs. A contact potential ( $\phi_0$ ) is created across the depletion region (also known as the space charge or transition region), this can be calculated from consideration of the conditions required for charge flow balance, [23]. Application of an external reverse bias extracts majority carriers from the n<sup>+</sup> and p regions at the space charge boundaries expanding its width. The space charge region behaves like a capacitor with an increasing plate separation. The reverse biased diode is normally modeled by a non-linear capacitance:

C(0) 3.1-3  $C_{dep}(V_d) = \left[1 - \frac{V_d}{\phi_0}\right]^m$   $C_{dep}(V_d) - \text{Depletion Capacitance}$   $C(0) - \text{Zero Bias Capacitance} (V_d = 0)$   $V_d - \text{Diode Voltage}$   $\phi_0 - \text{Contact Potential(approx. 0.5 V for power diodes)}$  m - Grading Coefficient

The grading coefficient depends abruptness of the junction. An abrupt junction has an m = 1/2 whereas a linearly graded junction has m = 1/3. High voltage diodes naturally tend to be fabricated with a graded junction. For diodes with  $V_{\rm rrm} >$ 500V m should be 1/3 [20-22, 28-29] manufacturers often do not quote the diode capacitance in data sheets. In the case where it is given it is often not measured at zero bias, though C(0) can easily be calculated using the above equation. When it is not given a simple rule of thumb can be used, [22-22];

$$C(0) = 12 I_{av}(rated) pF$$

3.1–4

This is a reasonable estimate for Fast and Ultra Fast Diodes in the  $I_{av} < 100A$ ;  $V_{rrm} < 1000V$  range. This is based on examination of data for many diodes. Under steady state reverse bias conditions a reverse current flows due to minority carrier flow. Because the minority carrier densities are low in the reverse biased condition this current is low except when the reverse voltage approaches the breakdown level. Reverse breakdown occurs when the electric field reaches a level at which minority carriers gain sufficient energy during the drift process to excite additional minority carriers to the conduction energy band. These in turn can excite further carriers. This is known as avalanche multiplication and the result being a sharp rise in reverse current for only small increases in voltage. If this is not limited destruction of the diode results. Some power semiconductors are designed to avalanche to a certain extent and therefore act to absorb transient turnoff energy in power electronic circuits, such a device is the Philips BYX30 fast rectifier diode, [22].

When forward bias is applied the depletion region shrinks allowing electrons from the  $n^+$  region to spill (injected) into the p region.

In the analysis that follows it is assumed that all conduction originates from electrons transiting to the p region, this is valid because equilibrium electron concentration in the  $n^+$  region is far higher than the equilibrium hole concentration in the p region. Once in the p region electrons become minority carriers. The minority carrier density at the transition area boundary will increase which in turn causes a concentration gradient into the p region. A minority carrier diffusion current into the p region results. Because the minority carrier concentration is now above the equilibrium level there is a natural tendency to return to equilibrium, this occurs by what is known as recombination. That is minority carriers recombine with majority carriers. The recombination rate is proportional to, the excess minority carrier concentration above the equilibrium level:

$$R_n = \frac{n_{pe}}{\tau_d}$$

3.1–5

$R_n$  – Minority carrier concentration recombination rate

n<sub>pe</sub> - Excess electron concentration in the p-region

$\tau_{\rm d}$  – Excess minority carrier lifetime

The minority carrier life time represents the average time between recombinations, [23]. The excess minority carrier concentration will build up throughout the p region until a balance between injected minority carrier flow and the recombination flow is established. The minority carrier concentration from the transition boundary to the ohmic contact can be solved for using this balance condition. Where the p region, which in this case is termed the base of the diode, is long compared with the average distance travelled by a minority carrier before recombination the profile of the concentration is exponential as shown in Figure 3-1.

This can be easily understood by realising that minority carrier conduction is occurring via diffusion which is proportional to the concentration gradient. At any point this current is balanced by the recombination current which is proportional to the concentration. Therefore the concentration gradient must reduce with the concentration level which implies an exponential relationship. If the base of the diode is short compared with the minority carrier travel before recombination (short based diode) then most carriers do not recombine before reaching the ohmic contact. The minority carrier lifetime now becomes the transit time through the base region. The short based diode is assumed in the SPICE model and the minority carrier lifetime has been called the Transit Time  $(T_t)$ . The carrier concentration is assumed to linearly decrease towards the ohmic contact, [23]. Real diodes will be something between the two cases, but this detailed knowledge is not necessary for our purposes. The minority carrier injection is normally classified into three levels, low level, medium level and high level. This relates to the minority carrier concentration. Low level injection is characterised by the minority carrier concentration being small compared with the majority carrier concentration. There is a strong tendency to maintain space charge neutrality in the p region which is governed by the following:

$$N_a + n_p = p_p \qquad \qquad 3.1-6$$

# Na - Accepter atom concentration

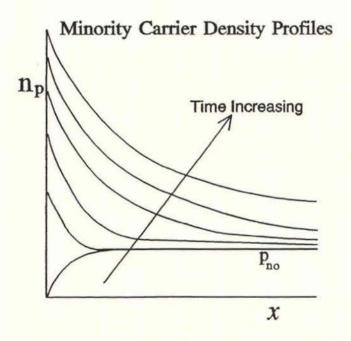

Since  $n_p \ll N_a$  for low level injection the effect of increases in  $n_p$  on  $p_p$  are neglected. Of cause what actually happens is there is a tendency for the increased minority carrier profile to be matched by an increased majority carrier profile. This is driven by an electric field in the p region directed towards the  $n^+$  region. A drift of holes occurs towards the transition region to balance the charge from the injected electrons. Some equilibrium field and majority carrier concentration is reached.