# A UPFC WITH REDUCED DC BUS CAPACITANCE FOR VOLTAGE REGULATION AND PHASE BALANCING IN LV DISTRIBUTION

NETWORKS WITH HIGH PV PENETRATIONS

Md. Mejbaul Haque, B. Sc. Eng. (EEE), M.Sc. Eng. (EEE)

Dissertation submitted in fulfilment of the requirement for the degree of Master of Engineering (M. Eng.)

School of Engineering and Technology

Central Queensland University

Rockhampton

Australia

30 October 2015

#### **ABSTRACT**

The penetration level of photovoltaic (PV) power in the low voltage (LV) distribution networks is rapidly increasing. The European Photovoltaic Industry Association reported the installed capacity of PV systems globally reached 177GW at the end of 2014. The annual rate of installations, 38.7GW in 2014, continues to increase. A large part of this is installed as residential systems connected to LV networks. The Australian Clean Energy Regulator has published a report showing the total installed capacity of PV in Australia exceeded 4.5GW in 2015. The impacts of high PV penetrations in LV residential distribution networks include voltage rise, voltage unbalance, and reverse power flow which may limit the level of photovoltaic penetration within the LV distribution networks. A four-leg compensator based on a unified power flow controller (UPFC) concept is proposed for simultaneous voltage and current compensation in LV distribution systems. As a voltage compensator, this compensation device is shown to be capable of regulating the positive, negative and zero sequence voltage in LV distribution networks under high PV penetrations. At the same time, as a current compensator, the device is capable of power factor correction, zero sequence or neutral current compensation, harmonic current compensation and a degree of negative sequence current compensation.

Instantaneous reactive power theory shows that DC-bus capacitor power will fluctuate at twice mains frequency during any unbalanced operation of the regulator. Real and instantaneous power balance of the UPFC can be maintained by allowing the input shunt converter to draw a small positive and negative sequence current respectively. Instantaneous power balance with negative sequence current makes it possible to reduce the DC bus capacitance which allows long life ceramic or polypropylene capacitors to replace electrolytic capacitors.

The operation of the proposed UPFC based four-leg compensator has been demonstrated by extensive simulation studies. These confirm that the device can perform the full range of series and parallel compensation duties for the compensation of voltage and current respectively. It has also been demonstrated that the DC bus voltage can be controlled using relatively small DC bus capacitors. The simulation work is further confirmed by experimental work with a small scale laboratory model. The laboratory system used commercial inverter modules rated at 600V and 15A per phase to construct two inverters with four phase legs. These were configured as a parallel connected inverter and a series inverter with series voltage injection transformers. The four-leg inverters shared a common DC bus and were equipped with voltage and current transformers and controlled using a Texas Instruments Delfino processor.

## TABLE OF CONTENTS

| ABSTI       | RACT                                                                                              | ii    |

|-------------|---------------------------------------------------------------------------------------------------|-------|

| TABLI       | E OF CONTENTS                                                                                     | iv    |

| LIST C      | OF FIGURES                                                                                        | vii   |

| LIST C      | OF TABLES                                                                                         | x     |

| LIST C      | OF SYMBOLS                                                                                        | xi    |

| ACKN        | OWLEDGEMENTS                                                                                      | xvi   |

| DECLA       | ARATION                                                                                           | xvii  |

| PUBLI       | CATIONS                                                                                           | xviii |

| Chapter 1   | INTRODUCTION                                                                                      | 1     |

| 1.1. Distr  | ibuted generation and growth of PV                                                                | 1     |

| 1.2. Integ  | ration of distributed PV generation in LV distribution network                                    | 2     |

| •           | pensator for LV distribution networks with distributed PV generation: A Untroller (UPFC) Proposal |       |

| 1.4. Aims   | and objectives of the research                                                                    | 8     |

| 1.5. Organ  | nisation of the thesis                                                                            | 9     |

| 1.6. Conc   | lusion                                                                                            | 10    |

| Chapter 2   | LITERATURE REVIEW                                                                                 | 11    |

| 2.1. Introd | duction                                                                                           | 11    |

| 2.2. Recei  | nt historical advancement of cumulative PV installation                                           | 11    |

| 2.2.1.      | Global PV scenario                                                                                | 11    |

| 2.2.2.      | Australian PV scenario                                                                            | 13    |

| 2.3. Bene   | fits of high Solar PV penetrations                                                                | 15    |

| 2.4. Impa   | ct of high PV penetrations in LV distribution network                                             | 17    |

| 2.4.1.      | Voltage regulation                                                                                | 19    |

| 2.4.2.      | Voltage unbalance                                                                                 | 21    |

| 2.5. Com    | mercially available mitigation methods                                                            | 22    |

| 2.5.1.      | Reconductoring                                                                                    | 22    |

| 2.5.2.      | On-load tap changer                                                                               | 23    |

| 2.5.3.      | Fixed or switched capacitor                                                                       | 26    |

| 2.6. Emer   | ging mitigation methods                                                                           | 27    |

| 2.6.1.      | VAR control of PV inverters                                                                       | 27    |

| 262         | Distributed energy storage systems                                                                | 29    |

| 2.6.3.      | Coordinated control between utility equipment and PV inverter | 31 |

|-------------|---------------------------------------------------------------|----|

| 2.6.4.      | Dynamic voltage restorer                                      | 33 |

| 2.6.5.      | Distributed static compensator                                | 35 |

| 2.6.6.      | Unified power flow controller                                 | 36 |

| 2.7. Conv   | rerter topologies                                             | 38 |

| 2.8. Inver  | ter with reduced DC bus capacitance                           | 40 |

| 2.9. Resea  | arch gap                                                      | 41 |

| 2.10. Con   | clusion                                                       | 44 |

| Chapter 3   | MODELLING & CONTROL STRATEGY FOR A UPFC                       | 45 |

| 3.1. Intro  | duction                                                       | 45 |

| 3.2. Four-  | leg reduced DC bus capacitance UPFC                           | 45 |

| 3.3. Mode   | elling of the 4+4 leg UPFC in continuous time domain          | 46 |

| 3.4. Insta  | ntaneous power flow analysis through UPFC                     | 47 |

| 3.4.1.      | Voltage regulation                                            | 47 |

| 3.4.2.      | Active filtering                                              | 50 |

| 3.4.3.      | Ancillary services                                            | 52 |

| 3.5. Contr  | rol strategies for UPFC based compensator                     | 53 |

| 3.5.1.      | Voltage control strategy for series converter                 | 53 |

| 3.5.2.      | Power control strategy for shunt converter                    | 55 |

| 3.6. Conc   | lusion                                                        | 59 |

| Chapter 4   | SIMULATION RESULTS                                            | 60 |

| 4.1. Intro  | duction                                                       | 60 |

| 4.2. Appl   | ication of UPFC based compensator in LV distribution feeder   | 60 |

| 4.3. Simu   | lation results for UPFC based compensator                     | 62 |

| 4.3.1.      | UPFC with zero sequence current compensator                   | 62 |

| 4.3.2.      | UPFC with zero sequence and reactive current compensation     | 71 |

| 4.4. Appl   | ication of UPFC based compensator for active filtering        | 79 |

| 4.4.1.      | Simulation results for 4+4 leg UPFC based active filter       | 80 |

| 4.5. Conc   | lusion                                                        | 83 |

| Chapter 5   | HARDWARE AND EXPERIMENTAL RESULTS                             | 85 |

| 5.1. Intro  | duction                                                       | 85 |

| 5.2. Phase  | e locked loop                                                 | 86 |

| 5.3. Three  | e dimensional space vector modulation                         | 87 |

| 5.4. Expe   | rimental system architecture                                  | 94 |

| 5.5. Back   | ground resources                                              | 97 |

| 5.6. Filter | design considerations                                         | 97 |

| 5.7. Voltag | ge regulation and control of series converter of UPFC based compensator | 101 |

|-------------|-------------------------------------------------------------------------|-----|

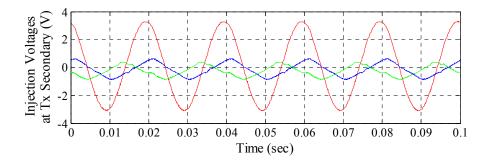

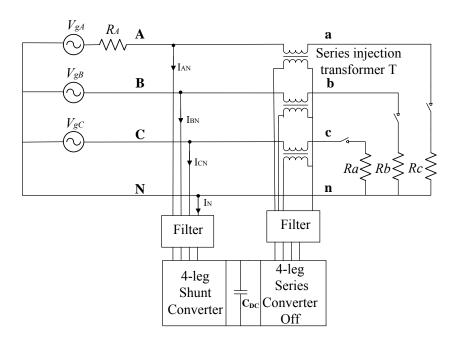

| 5.7.1.      | Experimental diagram for voltage regulation                             | 101 |

| 5.7.2.      | Closed loop control system for voltage regulation                       | 103 |

| 5.7.3.      | Experimental results for voltage regulation                             | 105 |

| 5.8. Curre  | nt regulation and control of shunt converter of UPFC based compensator  | 107 |

| 5.8.1.      | Experimental diagram for current regulation                             | 107 |

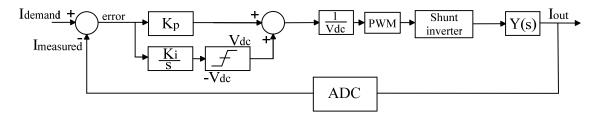

| 5.8.2.      | Closed loop control system for current regulation                       | 108 |

| 5.8.3.      | Experimental results for current regulation                             | 110 |

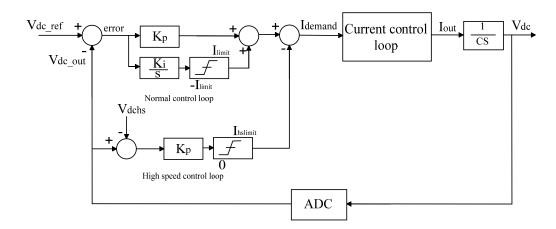

| 5.9. DC bu  | us voltage regulation system                                            | 115 |

| 5.9.1.      | Experimental diagram of the DC bus voltage regulation system            | 115 |

| 5.9.2.      | Closed loop control system for DC bus voltage regulation                | 116 |

| 5.9.3.      | Experimental results for DC Bus voltage regulator                       | 117 |

| 5.10. Cond  | clusion                                                                 | 119 |

| Chapter 6   | DISCUSSIONS, CONCLUSIONS AND FUTURE WORK                                | 122 |

| 6.1. Discu  | ssions                                                                  | 122 |

| 6.2. Concl  | usions                                                                  | 126 |

| 6.3. Future | e Work                                                                  | 128 |

| REFER       | ENCES                                                                   | 130 |

| Chapter 7   | APPENDIX A: DETAILS OF THE DEVELOPMENT BOARD                            | 140 |

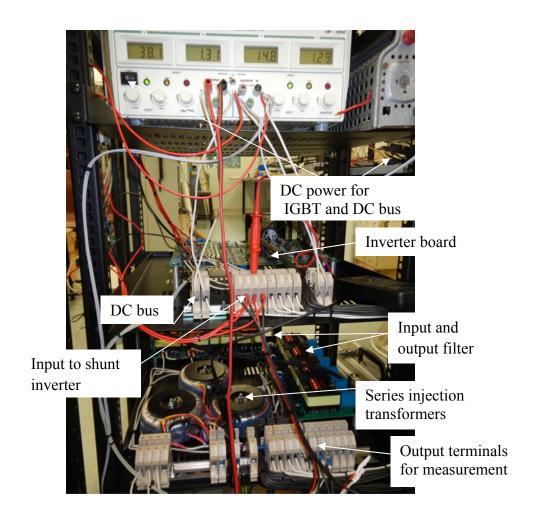

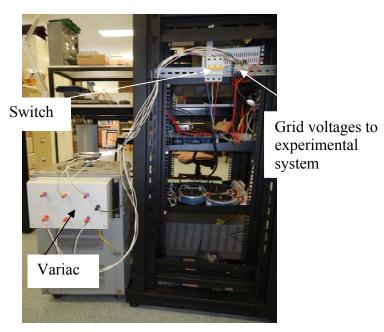

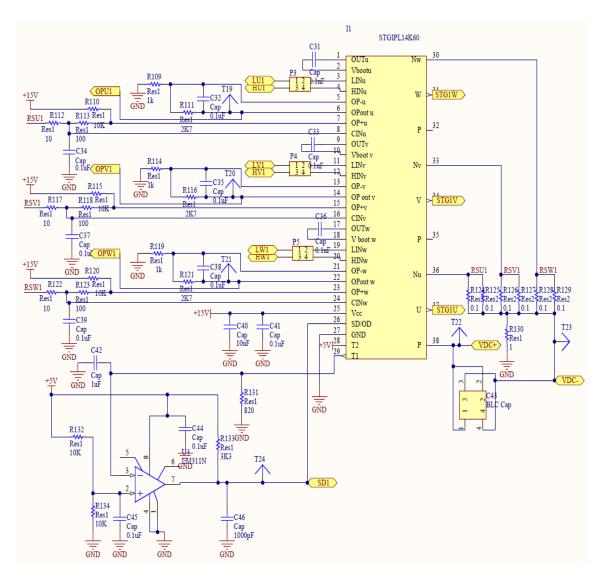

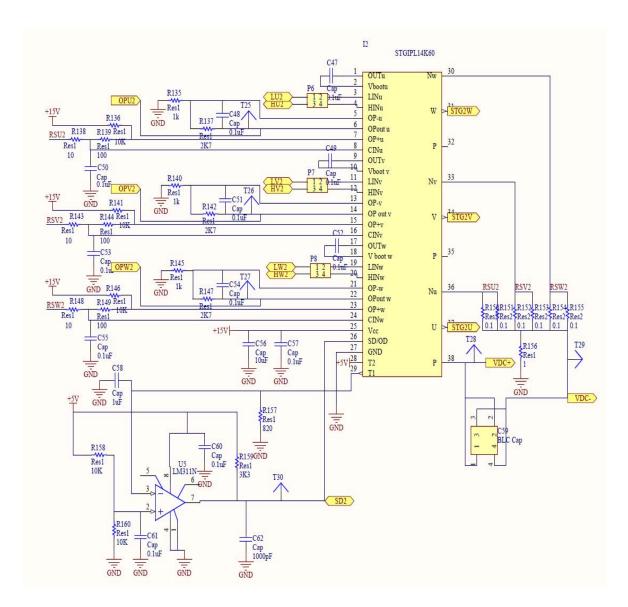

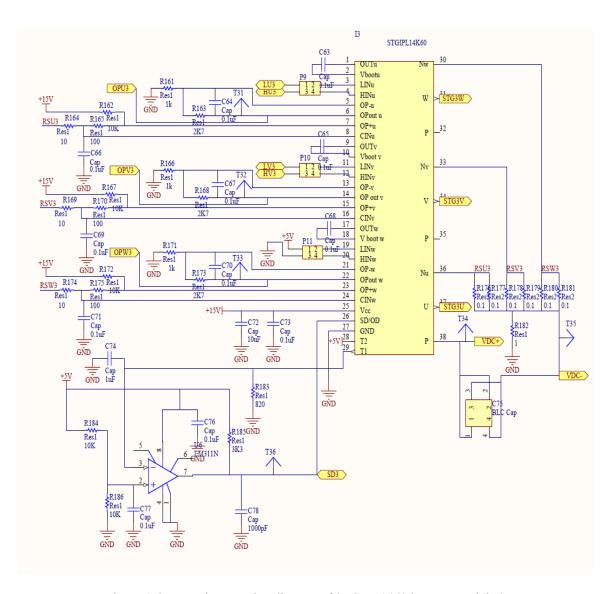

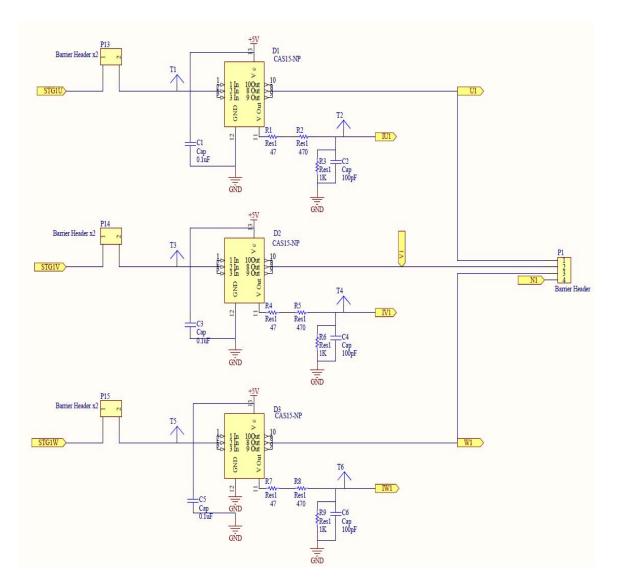

| A. 1        | The experimental development board                                      | 140 |

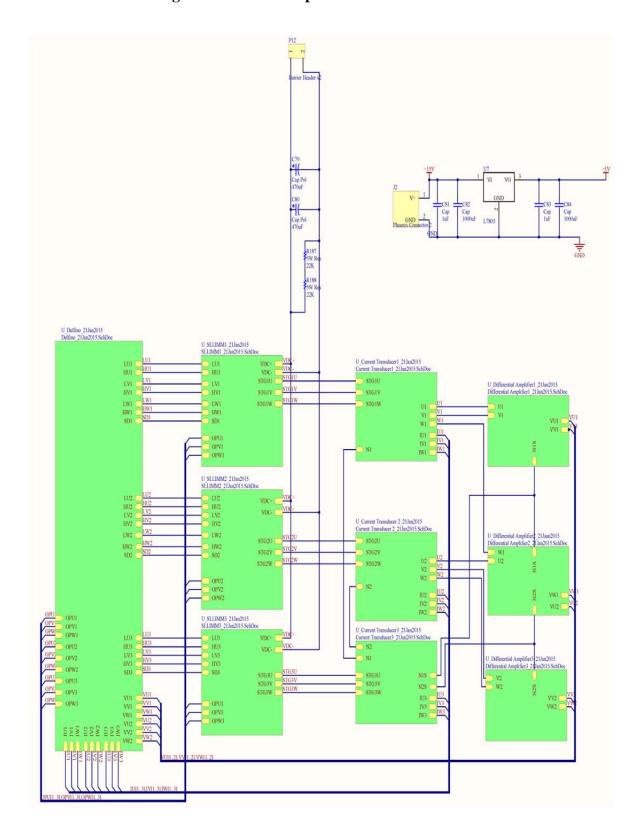

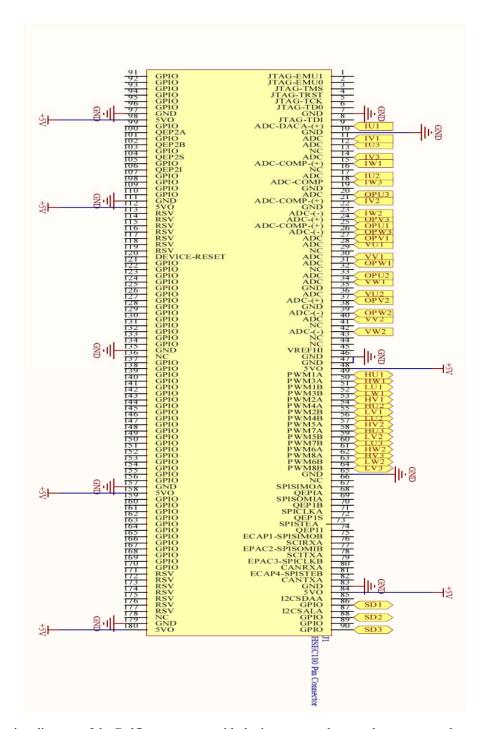

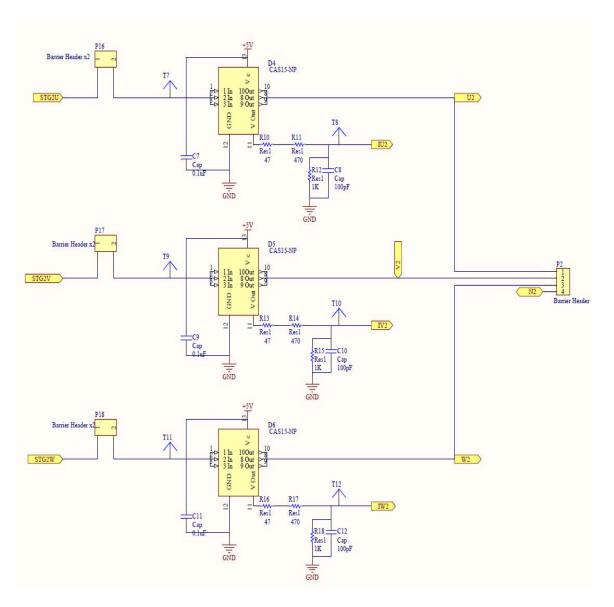

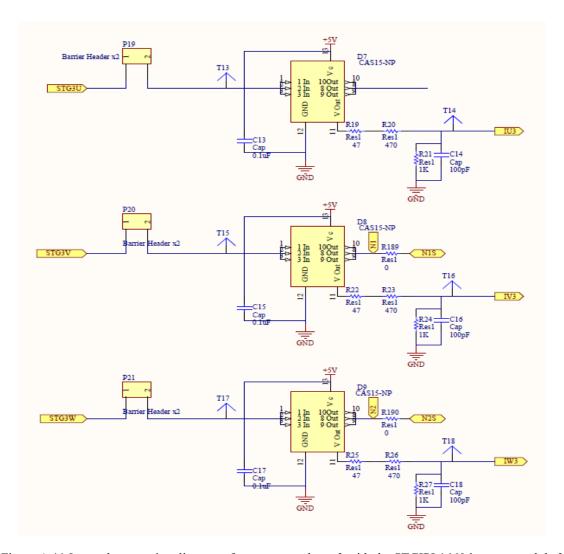

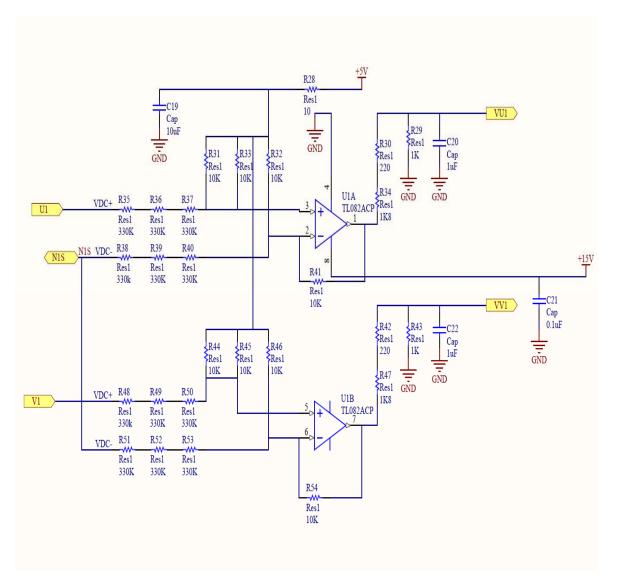

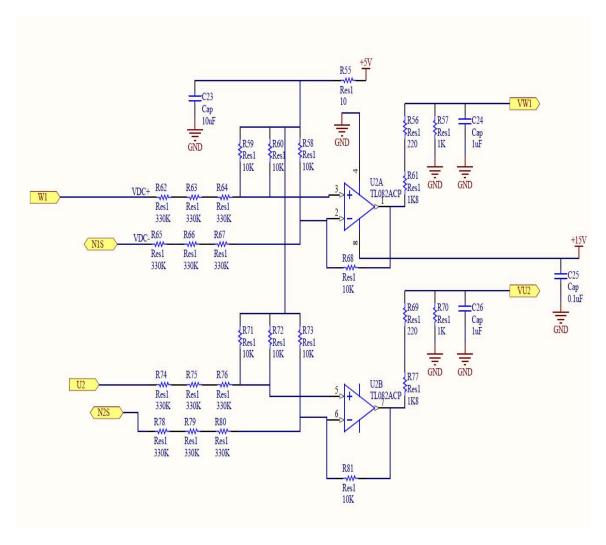

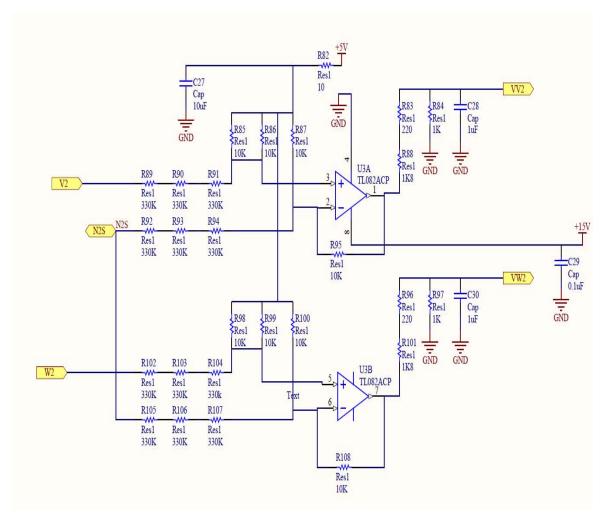

| A. 2        | Schematic diagrams of the development board                             | 143 |

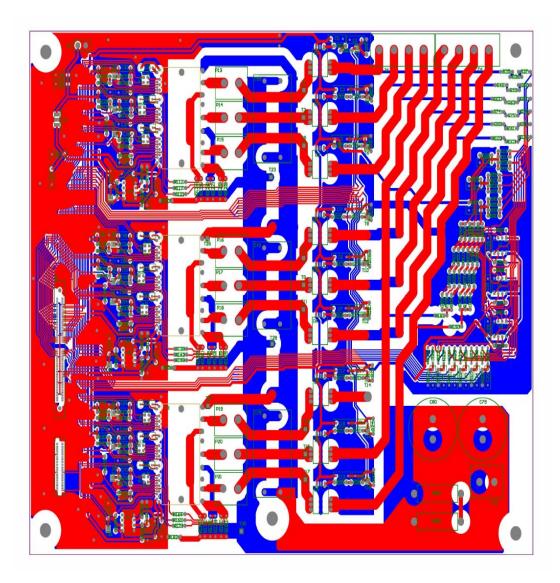

| A. 3        | PCB layout of the development board                                     | 155 |

## LIST OF FIGURES

| Figure 1.1 Schematic of unified power flow controller (UPFC) [21]                                           | 8   |

|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.1 Progress of total global cumulative installed PV capacity (2000-2014) [3, 22]                    |     |

| Figure 2.2 Progress of cumulative small scale installed PV capacity in Australia since April 2001 [4, 27]   |     |

| Figure 2.3 Single line diagram of a distribution network                                                    |     |

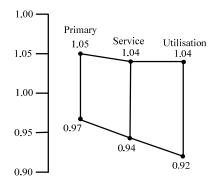

| Figure 2.4 The voltage range used in [12]                                                                   |     |

| Figure 2.5 Schematic of a typical on-load tap changing transformer construction                             |     |

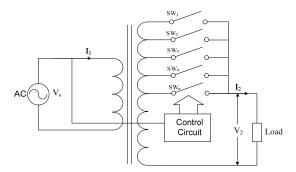

| Figure 2.6 Schematic of a fast on-load tap changing transformer construction                                |     |

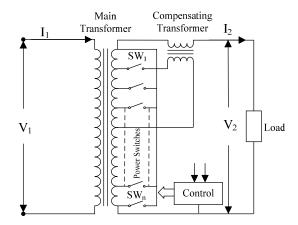

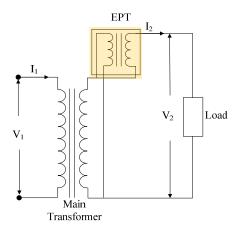

| Figure 2.7 Schematic of a fast and continuous on-load voltage regulator based on EPT                        |     |

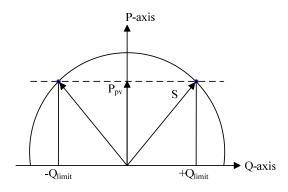

| Figure 2.8 Reactive power control capabilities of grid connected PV inverters [61]                          |     |

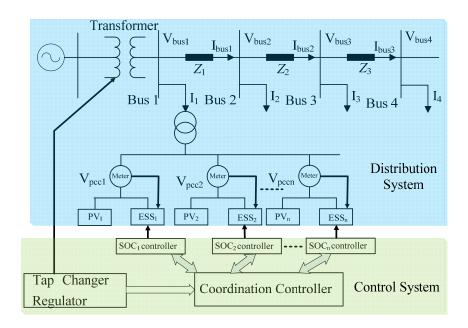

| Figure 2.9 Coordinated control of distributed ESS with tap changer transformers for voltage rise mitigation |     |

|                                                                                                             |     |

| Figure 2.10 Schematic of a DVR connected to a distribution network                                          |     |

| Figure 2.10 Schematic of a DVK connected to a distribution network                                          |     |

| Figure 2.12 Schematic of a UPFC connected to a distribution network                                         |     |

|                                                                                                             |     |

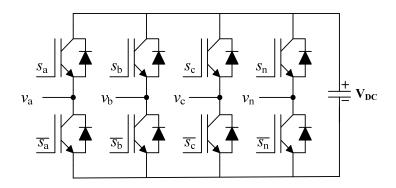

| Figure 2.13 Four-wire four-leg topology [100]                                                               |     |

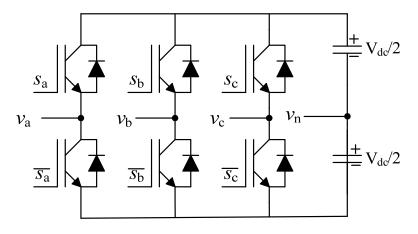

| Figure 2.14 Four-wire three-leg with split capacitor topology [100]                                         |     |

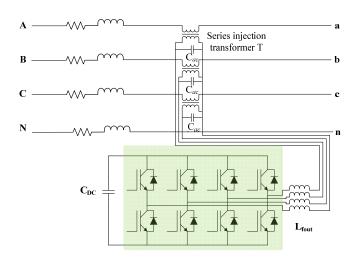

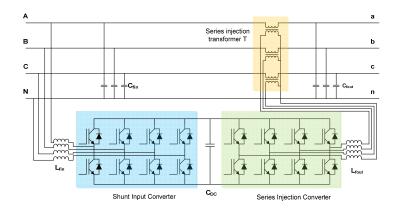

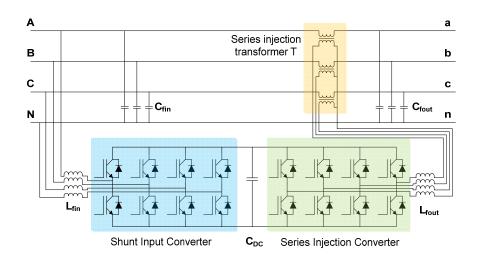

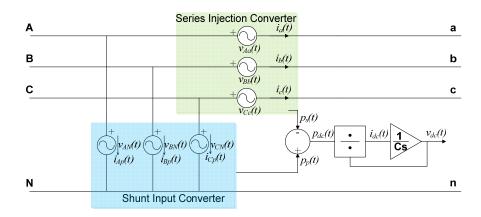

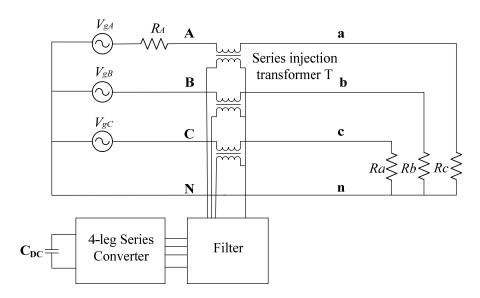

| Figure 3.1 A 4+4 leg UPFC based compensator with reduced DC bus capacitor                                   |     |

| Figure 3.2 Continuous time domain model of 4+4 leg UPFC based compensator [19]                              |     |

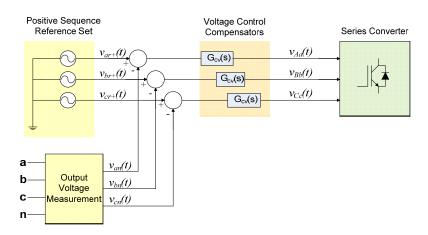

| Figure 3.3 Voltage control arrangement for the series converter of UPFC based compensator [19]              |     |

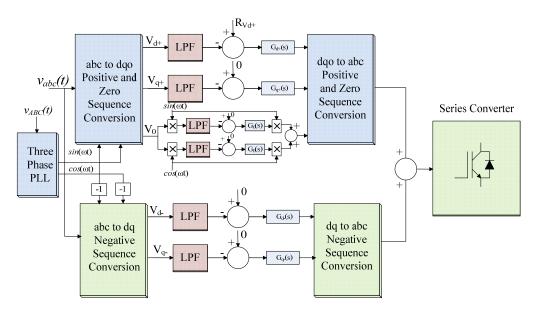

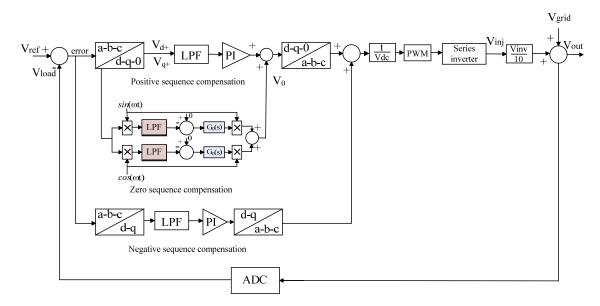

| Figure 3.4 Sequence based voltage control strategy for series converter of UPFC based compensator           |     |

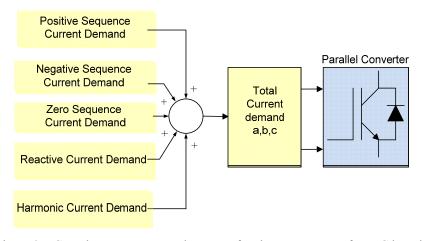

| Figure 3.5 Complete current control strategy for shunt converter of UPFC based compensator                  |     |

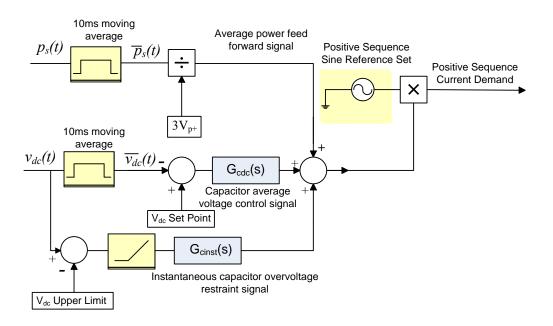

| Figure 3.6 Average power control arrangement                                                                |     |

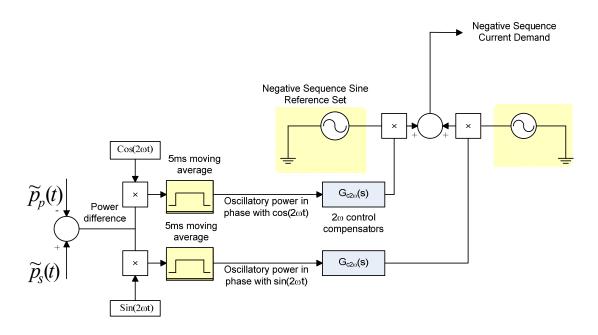

| Figure 3.7 2\omega oscillatory power control arrangement.                                                   |     |

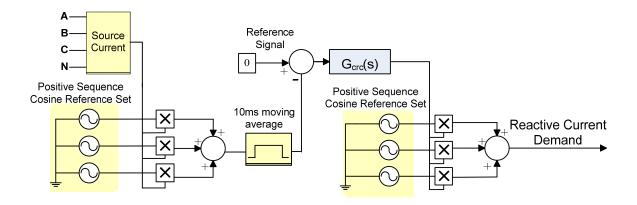

| Figure 3.8 Reactive current compensation arrangement.                                                       |     |

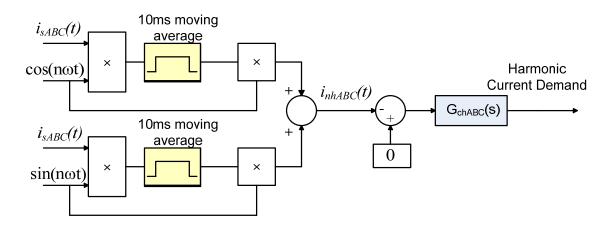

| Figure 3.9 Harmonic current reference detection and control arrangement.                                    |     |

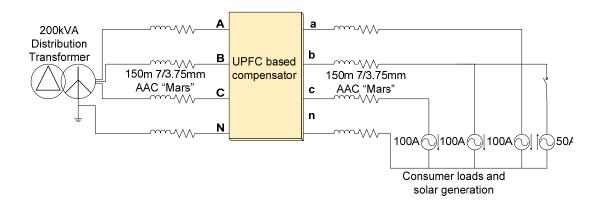

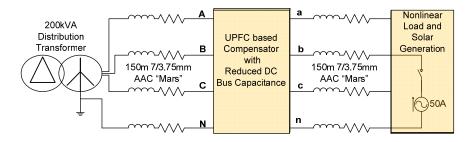

| Figure 4.1 Application of 4+4 leg UPFC based compensator in LV distribution feeders [19]                    |     |

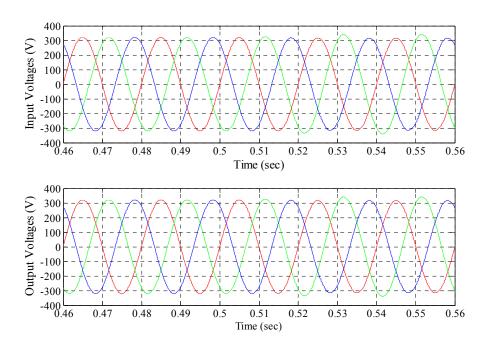

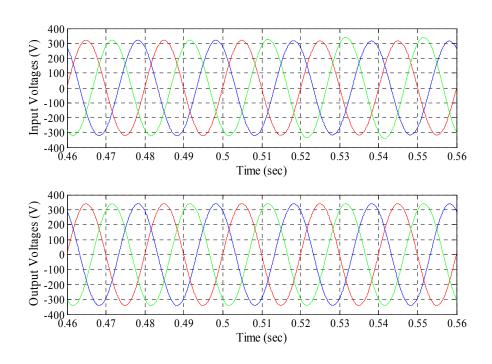

| Figure 4.2 Voltages at A,B,C,N input and a,b,c,n output terminals without UPFC based compensator            |     |

| Figure 4.3 Voltages at A,B,C,N input and a,b,c,n output terminals with UPFC based compensator               | 63  |

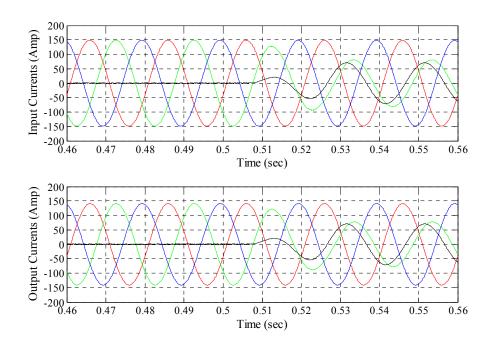

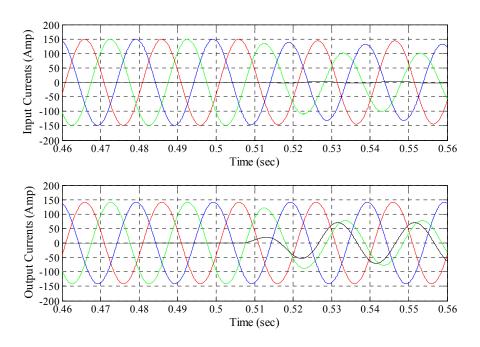

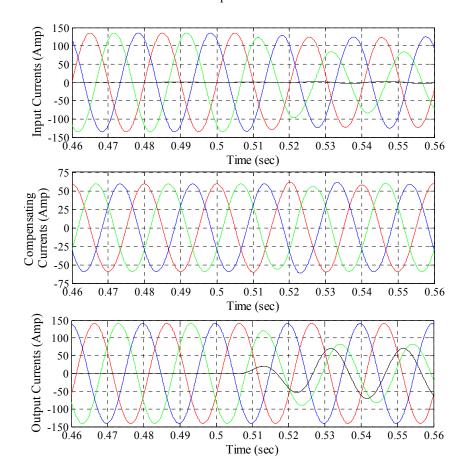

| Figure 4.4 Currents from A,B,C,N input and a,b,c,n output terminals of the UPFC based compensator           |     |

| without zero sequence current compensator                                                                   |     |

| Figure 4.5 Currents from A,B,C,N input and a,b,c,n output terminals of the UPFC based compensator with      |     |

| zero sequence current compensator                                                                           |     |

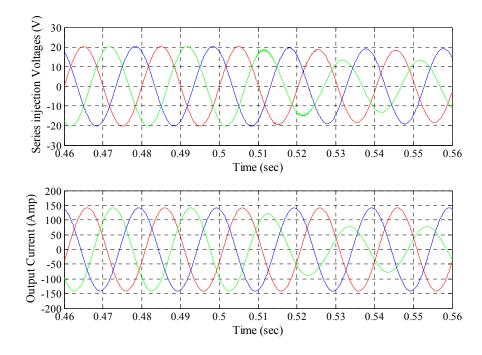

| Figure 4.6 Series injection voltages and output currents from terminals a,b,c,n                             |     |

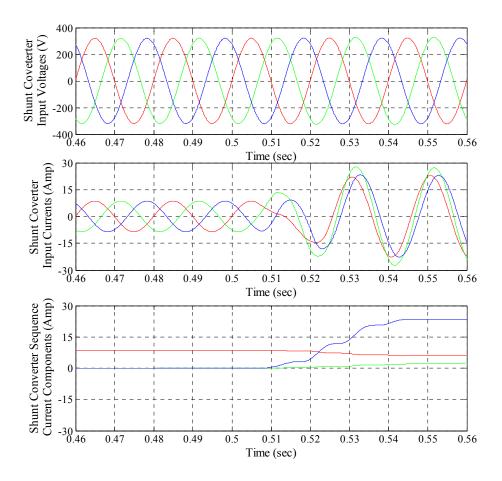

| Figure 4.7 Shunt converter input voltages and currents with their sequence components (+ve sequence, re-    |     |

| ve sequence, green, zero sequence, blue)                                                                    |     |

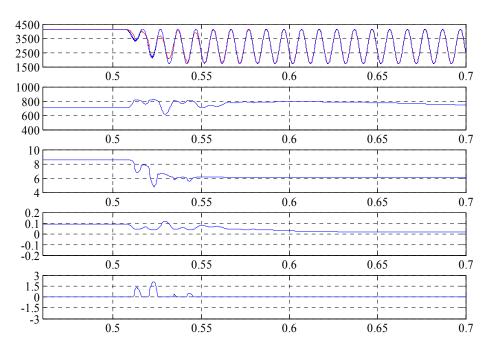

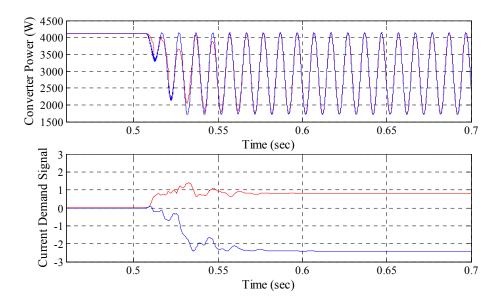

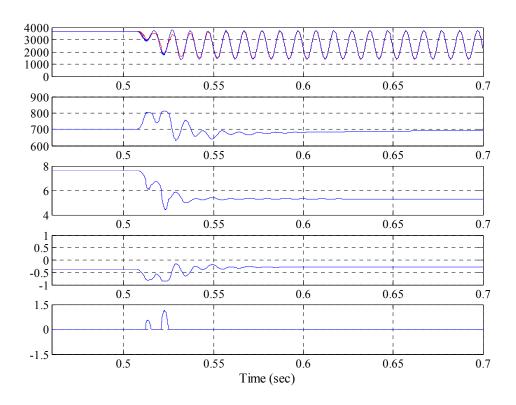

| Figure 4.8 Top traces: series converter power (blue) and shunt converter power (red). Other traces top to   |     |

| bottom: DC bus voltage; positive sequence current demand feed forward signal; DC bus voltage regulato       |     |

| current demand; Instantaneous bus voltage current demand                                                    |     |

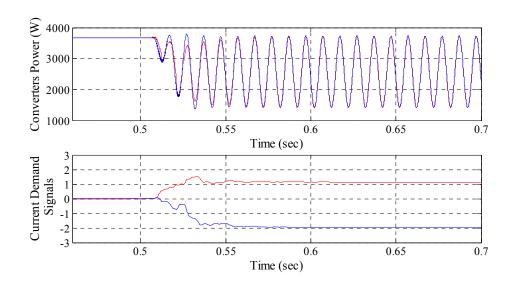

| Figure 4.9 Series converter power (blue) and shunt converter power (red), and current demand signals for    | r   |

| negative sequence cosine (blue) and sine (red) terms                                                        |     |

| Figure 4.10 Top traces: series converter power (blue) and shunt converter power (red). Other traces top to  | )   |

| bottom: DC bus voltage; positive sequence current demand feed forward signal; DC bus voltage regulato       | r   |

| current demand; Instantaneous bus voltage current demand                                                    |     |

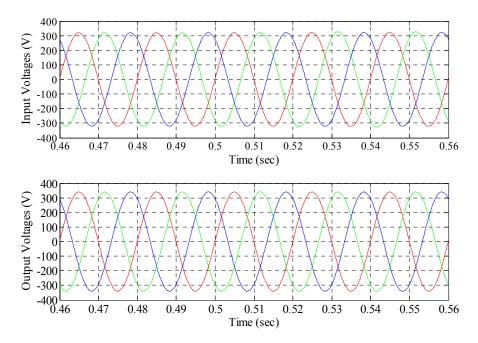

| Figure 4.11 Voltages at A,B,C,N input and a,b,c,n output terminals with zero sequence and reactive curre    | ent |

| compensation                                                                                                |     |

| Figure 4.12 Currents from A,B,C,N input and a,b,c,n output terminals and injected compensating current      |     |

| with zero sequence and reactive current compensator                                                         |     |

| Figure 4.13 Input voltages at terminals A,B,C,N and input currents from terminals A,B,C,N of the voltage    | e   |

| regulator with zero sequence and reactive current compensator                                               |     |

| Figure 4.14 Series injection voltages and output currents from terminals a,b,c,n                           | 75     |

|------------------------------------------------------------------------------------------------------------|--------|

| Figure 4.15 Shunt converter input voltages and currents with their sequence components (+ve sequence,      | red;   |

| -ve sequence, green; zero sequence, blue) with zero sequence and reactive current compensation             | 76     |

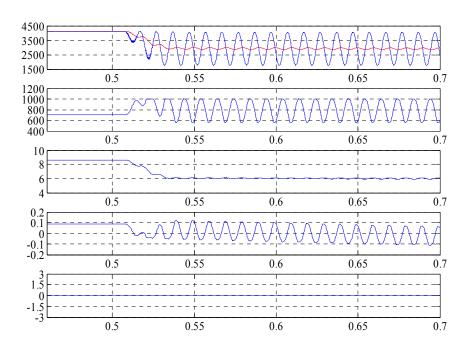

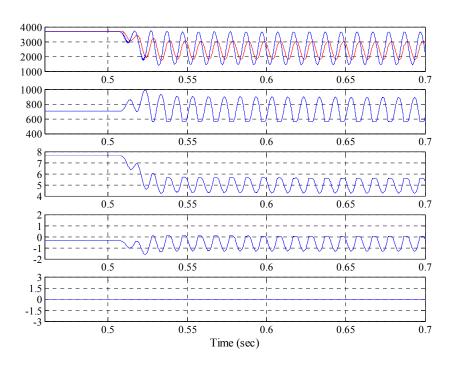

| Figure 4.16 Top traces: series converter power (blue) and shunt converter power (red). Other traces top t  | :0     |

| bottom: DC bus voltage; positive sequence current demand feed forward signal; DC bus voltage regulator     | or     |

| current demand; Instantaneous bus voltage current demand                                                   | 77     |

| Figure 4.17 Series converter power (blue) and shunt converter power (red), and current demand signals f    | for    |

| negative sequence cosine (blue) and sine (red) terms                                                       | 78     |

| Figure 4.18 Top traces: series converter power (blue) and shunt converter power (red). Other traces top t  | :0     |

| bottom: DC bus voltage; positive sequence current demand feed forward signal; DC bus voltage regulator     | or     |

| current demand; Instantaneous bus voltage current demand                                                   | 79     |

| Figure 4.19 Application of 4+4 leg UPFC based compensator for active filtering in LV distribution feeds    | ers 80 |

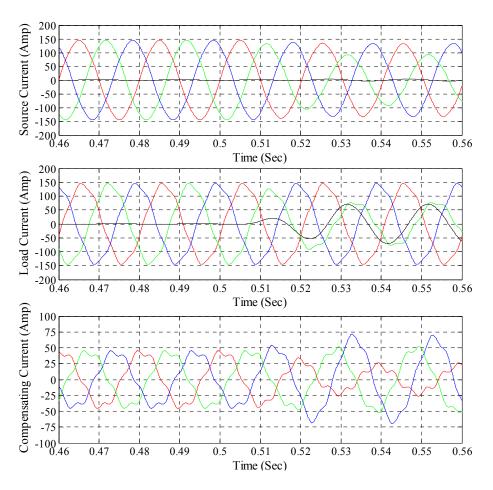

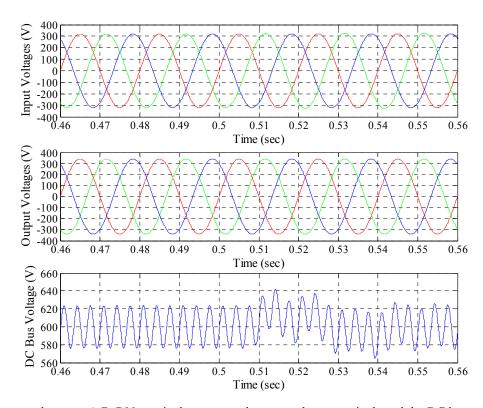

| Figure 4.20 Source currents from A,B,C,N input terminals, load currents from a,b,c,n output terminals at   | nd     |

| the compensating currents                                                                                  | 81     |

| Figure 4.21 Input voltages at A,B,C,N terminals, output voltages at a,b,c,n terminals and the DC bus vol   |        |

|                                                                                                            | 82     |

| Figure 5.1 PLL based on power measurement by two wattmeter method principle [121]                          |        |

| Figure 5.2 Dodecahedron that contains the control region, in abc coordinates, showing the switching vector |        |

| [100]                                                                                                      |        |

| Figure 5.3 Representation of some of the obtained tetrahedrons (a) Regions RP = 8 and RP = 57. (b) Reg     | gions  |

| RP = 13 and $RP = 52 [100]$                                                                                |        |

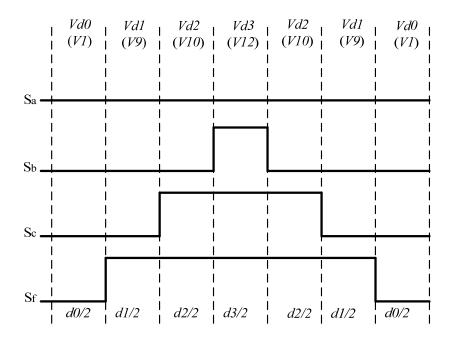

| Figure 5.4 Switching signals to produce a vector in region RP = 1                                          |        |

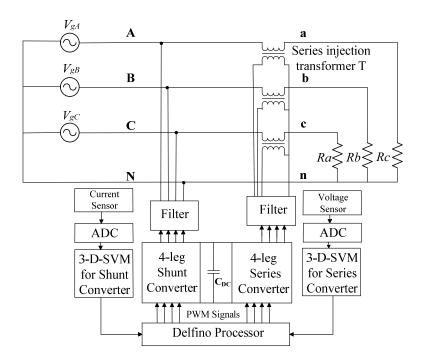

| Figure 5.5 Complete experimental system architecture for UPFC based voltage compensator                    | 95     |

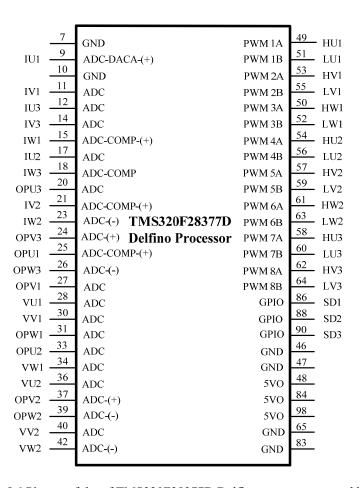

| Figure 5.6 Pin out of the of TMS320F28377D Delfino processor control board                                 | 96     |

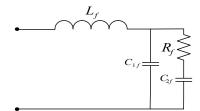

| Figure 5.7 Schematic for filter circuit used in the experimental system                                    |        |

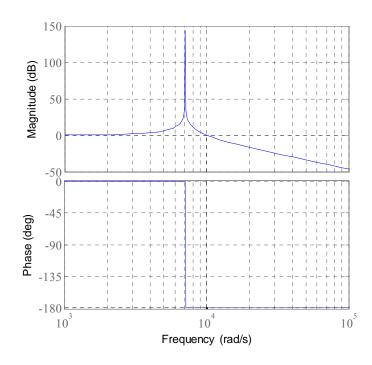

| Figure 5.8 Bode plot of the transfer function, <i>H</i> 1s of the undamped filter                          | 99     |

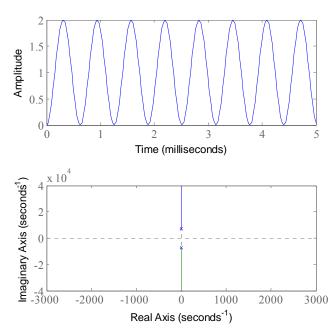

| Figure 5.9 Step response and root locus plot of the transfer function, <i>H</i> 1s of the undamped filter  | 100    |

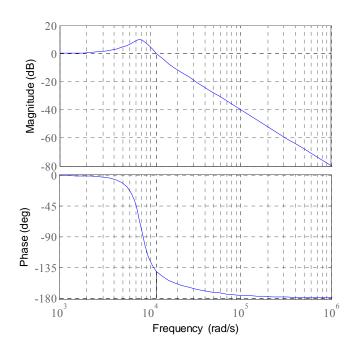

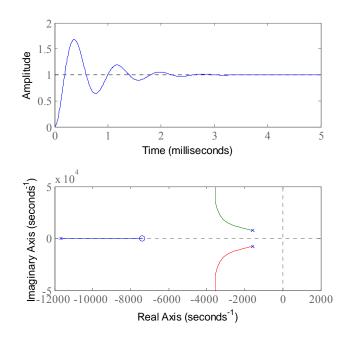

| Figure 5.10 Bode plot of the transfer function, <i>H2s</i> of the undamped filter                          | 100    |

| Figure 5.11 Step response and root locus plot of the transfer function, <i>H2s</i> of the undamped filter  | 101    |

| Figure 5.12 Experimental diagram of series converter of UPFC based compensator for voltage regulation      | n 102  |

| Figure 5.13 Closed loop control system used for voltage regulation in the experiment                       | 104    |

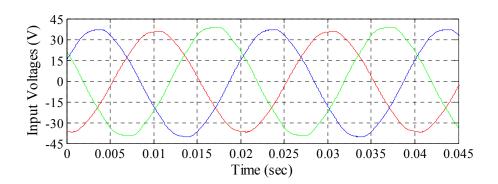

| Figure 5.14 Input voltages at A,B,C,N terminals of the voltage regulation system                           | 106    |

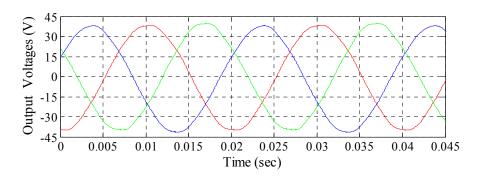

| Figure 5.15 Output regulated load voltage at a,b,c,n terminal of the voltage regulation system             | 106    |

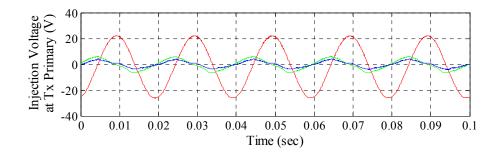

| Figure 5.16 Series converter output voltages at the transformer primary                                    | 107    |

| Figure 5.17 Series converter output voltages at the transformer secondary                                  | 107    |

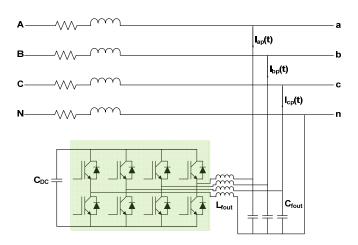

| Figure 5.18 Experimental diagram of shunt converter of UPFC based compensator for current regulation       |        |

| Figure 5.19 Closed loop control system used for current regulation in the experiment                       | 109    |

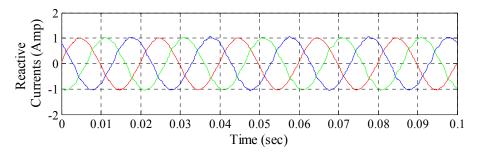

| Figure 5.20 Reactive currents when the grid is forced to draw capacitive currents                          | 111    |

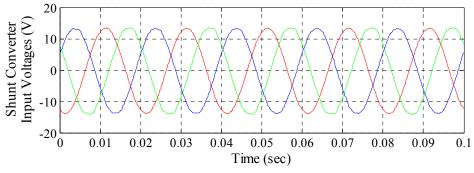

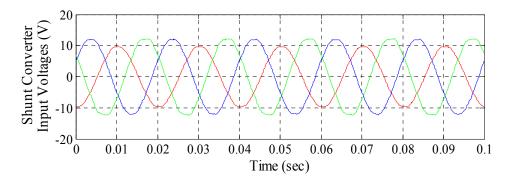

| Figure 5.21 Shunt converter input voltages while the grid is forced to draw capacitive currents            | 111    |

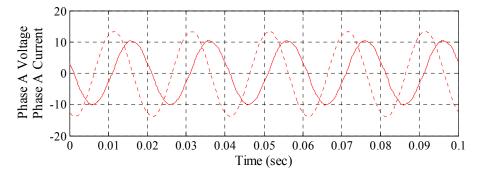

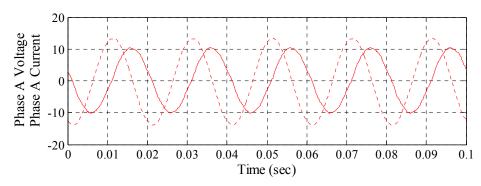

| Figure 5.22 Shunt converter phase A currents (red) and phase A voltage (dashed red) in force capacitive    |        |

| mode. The scale is 10V/div for voltage and 1A/div for current                                              | 111    |

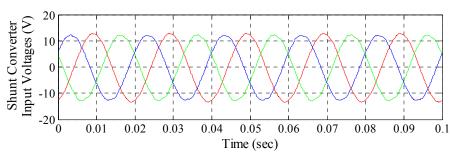

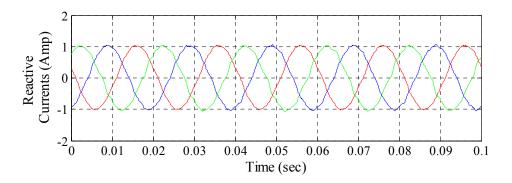

| Figure 5.23 Reactive currents when the grid is forced to draw inductive currents                           | 112    |

| Figure 5.24 Shunt converter input voltages while the grid is forced to draw inductive currents             |        |

| Figure 5.25 Shunt converter phase A currents (red) and phase A voltage (dashed red) in force inductive     | mode   |

| The scale is 10V/div for voltage and 1A/div for current                                                    | 113    |

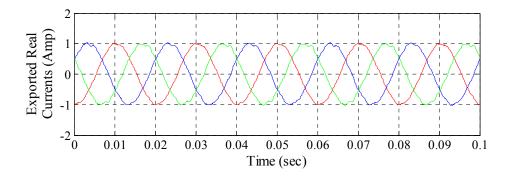

| Figure 5.26 Exported real currents to the grid by shunt converter                                          | 114    |

| Figure 5.27 Shunt converter input voltages while exporting real currents to the grid                       |        |

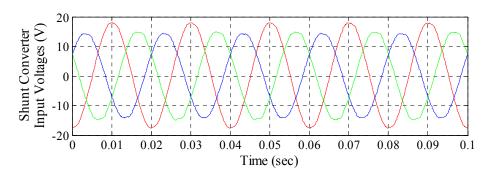

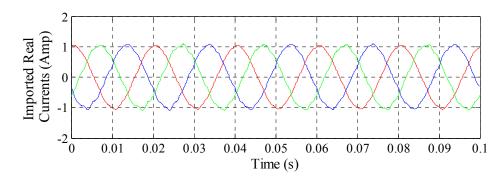

| Figure 5.28 Imported real currents from the grid by the shunt converter                                    |        |

| Figure 5.29 Shunt converter input voltages while importing real currents from the grid                     |        |

| Figure 5.30 Experimental diagram of UPFC based compensator for DC bus voltage regulation                   |        |

| Figure 5.31 Closed loop control system for DC bus voltage regulation                                       |        |

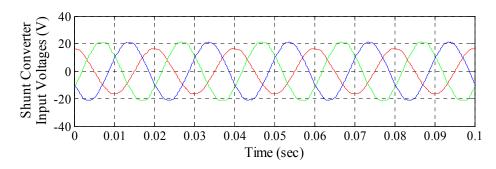

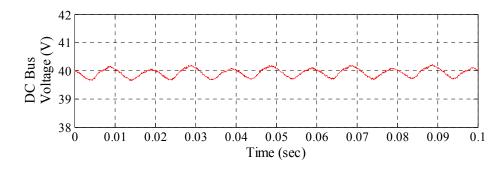

| Figure 5.32 Shunt converter input voltages during DC bus regulation from DC bus capacitor                  | 118    |

| Figure 5.33 Shunt converter input currents during DC bus regulation from DC bus capacitor                | . 118 |

|----------------------------------------------------------------------------------------------------------|-------|

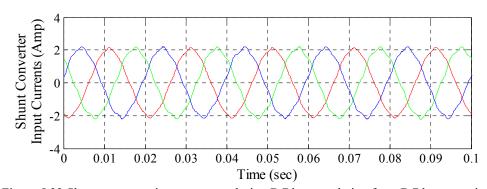

| Figure 5.34 DC bus voltage                                                                               | . 119 |

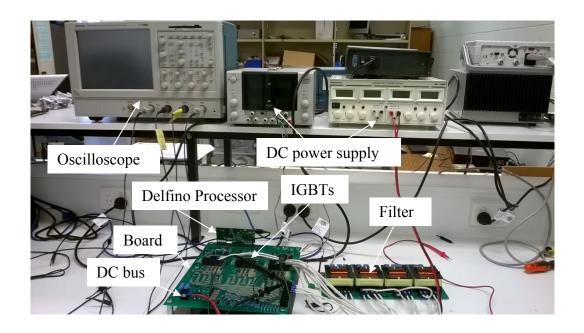

| Figure A.1 Photograph of the development board of UPFC based compensator under testing                   | . 140 |

| Figure A.2 View of the experimental set-up for UPFC based voltage compensator in the power engineering   | ng    |

| laboratory at CQUniversity                                                                               | . 141 |

| Figure A.3 View of the experimental set-up for UPFC based voltage compensator in the power engineering   | ng    |

| laboratory at CQUniversity                                                                               | . 141 |

| Figure A.4 Internal circuit diagram of the UPFC based compensator development board                      | . 143 |

| Figure A.5 Connection diagram of the Delfino processor with the inverters, voltage and current transduce | ers   |

|                                                                                                          | . 145 |

| Figure A.6 Internal connection diagram of STGIPL1460 inverter module 1                                   |       |

| Figure A.7 Internal connection diagram of STGIPL1460 inverter module 2                                   | . 147 |

| Figure A.8 Internal connection diagram of STGIPL1460 inverter module 3                                   | . 148 |

| Figure A.9 Internal connection diagram of current transducer 1 with the STGIPL1460 inverter module 1.    |       |

| Figure A.10 Internal connection diagram of current transducer 2 with the STGIPL1460 inverter module 2    | 2 150 |

| Figure A.11 Internal connection diagram of current transducer 3 with the STGIPL1460 inverter module 3    | 3 151 |

| Figure A.12 Internal connection diagram of high impedance differential voltage amplifier 1 with current  |       |

| transducer 1                                                                                             | . 152 |

| Figure A.13 Internal connection diagram of high impedance differential voltage amplifier 2 with current  |       |

| transducer 2                                                                                             | . 153 |

| Figure A.14 Internal connection diagram of high impedance differential voltage amplifier 3 with current  |       |

| transducer 3                                                                                             | . 154 |

| Figure A.15 PCB layout of the UPFC based compensator                                                     | . 155 |

# LIST OF TABLES

| Table 2.1 Global PV cumulative installed capacity and market share per region in 2013 and forward for | orecasts |

|-------------------------------------------------------------------------------------------------------|----------|

|                                                                                                       | 13       |

| Table 2.2 ANSI C84.1 Voltage Range for 120V voltage level [8]                                         | 19       |

| Table 2.3 Comparison between different energy storage devices [70, 73]                                | 30       |

| Table 4.1 PI controllers used in the simulation                                                       |          |

| Table 4.2 Different parameters used in the simulation and their values                                | 61       |

| Table 4.3 Input and output voltages and currents with zero sequence current compensation              | 70       |

| Table 4.4 Input and output voltages and currents with zero sequence current and reactive current      |          |

| compensation                                                                                          | 71       |

| Table 4.5 PI controllers used in the simulation                                                       | 80       |

| Table 4.6 Different parameters used in the simulation and their values                                | 80       |

| Table 5.1 Tuning parameters of the PLL                                                                | 87       |

| Table 5.2 Switching states, voltage terminals and switching vectors in abc coordinates [100]          | 88       |

| Table 5.3 Region pointer of the 24 tetrahedrons and their NZSV vectors [100]                          | 91       |

| Table 5.4 Summary of equations for duty cycle calculation [100]                                       | 93       |

| Table 5.5 Filter parameters used in the experimental system                                           | 99       |

| Table 5.6 List of resistors used in the experimental system.                                          | 103      |

| Table 5.7 Tuning parameters of voltage injection control loop                                         | 104      |

| Table 5.8 Measurement data from experimentally designed voltage regulation system                     | 106      |

| Table 5.9 Tuning parameters for current control loop for shunt converter                              | 109      |

| Table 5.10 Measurement data from experimentally designed current regulation system                    | 111      |

| Table 5.11 Measurement data from experimentally designed DC bus voltage regulation system             | 117      |

### LIST OF SYMBOLS

$i_s$  Source currents

$i_C$  Compensating currents

$v_C$  Compensating voltages

$C_{DC}$  DC bus capacitance

$V_{dc}$  Average DC bus capacitor voltage

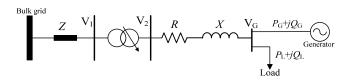

Z Feeder impedance

R Feeder resistance

*X* Feeder reactance

$V_1$  Transformer primary voltage

$V_2$  Transformer secondary voltage

$I_1$  Transformer primary current

*I*<sub>2</sub> Transformer secondary current

SW Switch

$V_G$  Grid voltages

$P_G$  Generator real power

$Q_G$  Generator reactive power

$P_L$  Load real power

$Q_L$  Load reactive power

EPT Electronic power transformer

$P_{pv}$  Real power supplied by PV

S Apparent power

$Q_{limt}$  Reactive power limit

$V_{bus}$  Bus voltage

$V_{pcc}$  Voltage at point of common coupling

$L_{fin}$  Input filter inductance

$L_{fout}$  Output filter inductance

$C_{fin}$  Input filter capacitance

$C_{fout}$  Output filter capacitance

$i_a(t)$  Line a current

$i_b(t)$  Line b current

| i (t)                                  | Line c current                                                         |

|----------------------------------------|------------------------------------------------------------------------|

| $i_c(t)$                               |                                                                        |

| $i_{Ap}(t)$                            | Shunt converter phase a input current                                  |

| $i_{Bp}(t)$                            | Shunt converter phase b input current                                  |

| $i_{Cp}(t)$                            | Shunt converter phase c input current                                  |

| $v_{Aa}(t)$                            | Series injection voltage at phase a                                    |

| $v_{Bb}(t)$                            | Series injection voltage at phase b                                    |

| $v_{cc}(t)$                            | Series injection voltage at phase c                                    |

| $i_s(t)$                               | Series converter instantaneous power                                   |

| $p_p(t)$                               | Shunt converter instantaneous power                                    |

| $p_{dc}(t)$                            | Instantaneous power at DC bus                                          |

| $i_{dc}(t)$                            | DC bus capacitor instantaneous current                                 |

| $v_{dc}(t)$                            | DC bus capacitor instantaneous voltage                                 |

| $\overline{p_s}$                       | Average component of series converter instantaneous power              |

| $\widetilde{p_{\scriptscriptstyle S}}$ | Oscillatory component of series converter instantaneous power          |

| $\overline{p_p}$                       | Average component of shunt converter instantaneous power               |

| $\widetilde{p_p}$                      | Oscillatory component of shunt converter instantaneous power           |

| $V_{s+}$                               | Positive sequence component of series injected voltage                 |

| $V_{s-}$                               | Negative sequence component of series injected voltage                 |

| $V_{s0}$                               | Zero sequence component of series injected voltage                     |

| $I_{s+}$                               | Positive sequence component of line current                            |

| $I_{s-}$                               | Negative sequence component of line current                            |

| $I_{s0}$                               | Zero sequence component of line current                                |

| $\varphi_{vs+}$                        | Phase angle of positive sequence component of series injection voltage |

| $arphi_{vs-}$                          | Phase angle of negative sequence component of series injection voltage |

| $arphi_{vs0}$                          | Phase angle of zero sequence component of series injection voltage     |

| $\varphi_{is+}$                        | Phase angle of positive sequence component of line current             |

| $arphi_{is-}$                          | Phase angle of negative sequence component of line current             |

| $arphi_{is0}$                          | Phase angle of zero sequence component of line current                 |

| $v_{AN}(t)$                            | Shunt converter input voltage at phase A to N                          |

| $v_{BN}(t)$                            | Shunt converter input voltage at phase B to N                          |

| $v_{CN}(t)$                            | Shunt converter input voltage at phase C to N                          |

| $V_{p+}$                               | Positive sequence component of shunt converter input voltage           |

| $V_{p-}$          | Negative sequence component of shunt converter input voltage                |

|-------------------|-----------------------------------------------------------------------------|

| $V_{p0}$          | Zero sequence component of shunt converter input voltage                    |

| $I_{p+}$          | Positive sequence component of shunt converter input current                |

| $I_{p-}$          | Negative sequence component of shunt converter input current                |

| $I_{p0}$          | Zero sequence component of shunt converter input current                    |

| $arphi_{vp+}$     | Phase angle of positive sequence component of shunt converter input voltage |

| $arphi_{vp-}$     | Phase angle of negative sequence component of shunt converter input voltage |

| $arphi_{vp0}$     | Phase angle of zero sequence component of shunt converter input voltage     |

| $arphi_{ip+}$     | Phase angle of positive sequence component of shunt converter input current |

| $arphi_{ip-}$     | Phase angle of negative sequence component of shunt converter input current |

| $arphi_{ip0}$     | Phase angle of zero sequence component of shunt converter input current     |

| $E_c$             | Energy stored at DC bus capacitor                                           |

| $V_U$             | Upper limit of voltage at DC bus capacitor                                  |

| $V_L$             | Lower limit of voltage at DC bus capacitor                                  |

| $i_{Ah}(t)$       | Instantaneous value of 5 <sup>th</sup> harmonic current through phase A     |

| $i_{Bh}(t)$       | Instantaneous value of 5 <sup>th</sup> harmonic current through phase B     |

| $i_{Ch}(t)$       | Instantaneous value of 5 <sup>th</sup> harmonic current through phase C     |

| $i_{nhABC}(t)$    | Instantaneous value of three phase harmonic current demand signal           |

| $I_{h-}$          | Peak value of 5 <sup>th</sup> harmonic current                              |

| $arphi_{ih-}$     | Phase angle of the 5 <sup>th</sup> harmonic current                         |

| $p_h(t)$          | 5 <sup>th</sup> harmonic instantaneous power                                |

| $\widetilde{p_h}$ | 5 <sup>th</sup> harmonic average power                                      |

| $\overline{p_h}$  | 5 <sup>th</sup> harmonic oscillatory power                                  |

| τ                 | Time period of a cosine waveform for half cycle                             |

| T                 | Time period of a cosine waveform for full cycle                             |

| ω                 | Angular frequency in rad/s                                                  |

| $v_{ar+}(t)$      | Positive sequence instantaneous voltage reference for phase A               |

| $v_{br+}(t)$      | Positive sequence instantaneous voltage reference for phase B               |

| $v_{cr+}(t)$      | Positive sequence instantaneous voltage reference for phase C               |

| $v_{an}(t)$       | Instantaneous output voltage reference at phase A                           |

| $v_{bn}(t)$       | Instantaneous output voltage reference at phase B                           |

| $v_{cn}(t)$       | Instantaneous output voltage reference at phase C                           |

| $v_{abc}(t)$            | Three phase instantaneous output voltage                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|

| $v_{ABC}(t)$            | Three phase instantaneous input voltage                                                                           |

| $V_{d+}$                | Positive sequence d-axis voltage component                                                                        |

| $V_{q+}$                | Positive sequence q-axis voltage component                                                                        |

| $V_0$                   | Positive sequence 0-axis voltage component                                                                        |

| $V_{d-}$                | Negative sequence d-axis voltage component                                                                        |

| $V_{q-}$                | Negative sequence q-axis voltage component                                                                        |

| $R_{vd+}$               | Reference real voltage set point for d-axis                                                                       |

| $G_{d+}(s)$             | PI type positive sequence voltage compensator for d-axis                                                          |

| $G_{q+}(s)$             | PI type negative sequence voltage compensator for q-axis                                                          |

| $G_0(s)$                | PI type zero sequence voltage compensator for 0-axis                                                              |

| $G_{d-}(s)$ $G_{q-}(s)$ | PI type positive sequence voltage compensator for d-axis PI type negative sequence voltage compensator for q-axis |

| $G_{cdc}(s)$            | PI type DC bus voltage compensator                                                                                |

| $G_{cinst}(s)$          | P type instantaneous capacitor voltage restraint signal                                                           |

| $G_{c2\omega}(s)$       | PI type 2ω oscillatory power compensator                                                                          |

| $G_{crc}(s)$            | PI type reactive current compensator                                                                              |

| $G_{chABC}(s)$          | PI type three phase harmonic current compensators                                                                 |

| $R_a C$                 | Cosine reference signal for phase A                                                                               |

| $R_b C$                 | Cosine reference signal for phase B                                                                               |

| $R_c C$                 | Cosine reference signal for phase C                                                                               |

| $R_a S$                 | Sine reference signal for phase A                                                                                 |

| $R_a S$                 | Sine reference signal for phase B                                                                                 |

| $R_a S$                 | Sine reference signal for phase C                                                                                 |

| $v_{ab}$                | Line voltage between phase a and b                                                                                |

| $v_{cb}$                | Line voltage between phase c and b                                                                                |

| $arphi_e$               | Phase error                                                                                                       |

| $K_p$                   | Proportional gain of PI controller                                                                                |

| $K_i$                   | Integral gain of PI controller                                                                                    |

| $S_f$                   | Switching states for the phase leg f                                                                              |

| $s_a$                   | Switching states for the phase leg a                                                                              |

| $S_b$                   | Switching states for the phase leg b                                                                              |

| $S_C$                   | Switching states for the phase leg c                                                                              |

|                         |                                                                                                                   |

$v_{af}$  Four-leg inverter phase a to neutral voltage

$v_{bf}$  Four-leg inverter phase b to neutral voltage

$v_{cf}$  Four-leg inverter phase c to neutral voltage

$v_{a\_ref}$  Reference voltage vectors normalised with  $V_{dc}$  at phase a

$v_{b\_ref}$  Reference voltage vectors normalised with  $V_{dc}$  at phase b

$v_{c\_ref}$  Reference voltage vectors normalised with  $V_{dc}$  at phase c

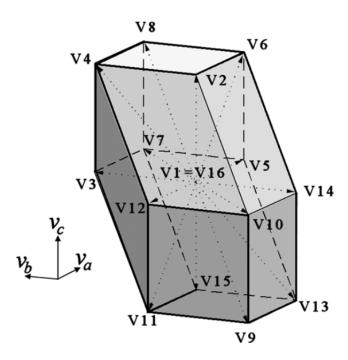

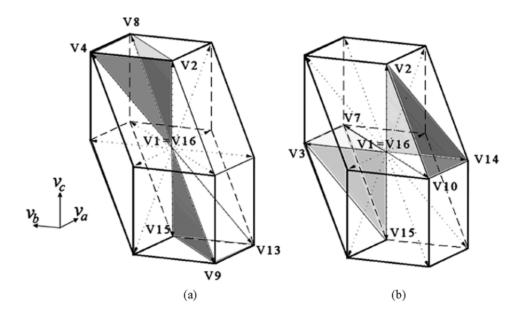

$V_1$  to  $V_{16}$  Switching vectors for different switching states

RP Range pointer

$d_i$  Duty cycle

$R_A$  Resistor connected with phase A at the grid side

$R_a$  Load resistor connected with phase A

$R_b$  Load resistor connected with phase B

$R_c$  Load resistor connected with phase C

$R_f$  Filter resistance

$L_f$  Filter inductance

$C_{1f}$  and  $C_{2f}$  Filter capacitance

$V_{qA}$  Grid voltage at phase A

$V_{qB}$  Grid voltage at phase B

$V_{qC}$  Grid voltage at phase C

$V_{AN}$  Input terminal voltage at phase A to N

$V_{BN}$  Input terminal voltage at phase B to N

$V_{CN}$  Input terminal voltage at phase C to N

$V_{an}$  Output load voltage at phase a to n

$V_{bn}$  Output load voltage at phase b to n

$V_{cn}$  Output load voltage at phase c to n

*I<sub>real</sub>* Shunt converter real current

$I_{reactive}$  Shunt converter reactive current

$I_{a\_demand}$  Phase a current demand for shunt converter

$I_{b\_demand}$  Phase b current demand for shunt converter

$I_{c\_demand}$  Phase c current demand for shunt converter

### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my principal supervisor Professor Peter Wolfs. Without his encouragement and guidance, completing this thesis on such a timely schedule certainly would not have been possible. I thank him for introducing me to the exciting field of power electronics and for bringing me into the School of Engineering & Technology family at CQUniversity. Professor Wolfs has given me a truly invaluable experience during my time at CQUniversity for which I am greatly indebted.

I gratefully acknowledge Assoc. Prof. Dr. Preethi Chandra for his support in giving me valuable and productive advice throughout my research. I would also like to thank Ben Sneath for his assistance in all aspects of the research, especially in the laboratory work that has been so important to this thesis. I wish to thank my other friends who have made my experience at SET more than just academic. My sincere appreciation is also given to Tim Mcsweeney for providing proof-reading service.

Most importantly, I would like to thank my parents and my wife for everything they have done for me. They have pushed me throughout my academic career, and I certainly owe all of my success to their loving support and guidance.

### **DECLARATION**

The research and discussion presented in this thesis are the original work of the author and has not been submitted at any tertiary institute or University for any other award. Any material with has been presented by any person or institute is duly referenced, and a complete list of all references is presented in the bibliography.

Md. Mejbaul Haque

### **PUBLICATIONS**

The following publications have been produced during the course of this thesis:

[1] M. Mejbaul Haque and P. Wolfs, "A four-wire reduced bus capacitance UPFC for LV distribution networks with high PV penetrations," in 2014 Australasian Universities Power Engineering Conference (AUPEC), Perth, Australia, 28 September - 1 October 2014, pp. 1-7.

Statement of Author Contribution:

In this work, the capability of four-wire UPFC with reduced DC bus capacitance for voltage regulation and neutral current compensation in LV distribution networks is explored. As an author, I developed the modeling and instantaneous power flow equations for four-leg UPFC in continuous domain. I designed the control methodologies for the series and shunt converter equipped zero sequence current compensator. I built and simulated the model using Matlab Simulink software. The simulation data was recorded and plotted using Matlab programming.

[2] M. Mejbaul Haque and P. Wolfs, "A Reduced Capacitance UPFC with Active Filtering Capability for High PV Penetration Applications," in *IEEE PES Asia-Pacific Power and Energy Engineering Conference 2015 (IEEE PES APPEEC 2015)*, Brisbane, Australia, 15 - 18 November 2015 (Accepted).

Statement of Author Contribution:

In this work, the active filtering capability of a reduced bus capacitance unified power flow controller (UPFC) is explored. In addition, I demonstrated the other capabilities such as voltage regulation and reactive current compensation. As an author, I developed the control models for UPFC based active filter. I was responsible for the control designs, simulation results and the discussions of the results. The simulation studies are carried out using Matlab Simulink.

### **Chapter 1 INTRODUCTION**

### 1.1. Distributed generation and growth of PV

Distributed generators are smaller and numerous sources of electrical power connected either directly to the distribution network or on the customer side of the meter [1]. Distributed generation generally tends to provide small scale power generation, while large centralised power plants supply the majority of the nation's power. Distributed energy systems are capable of generating electricity on or close to the site where that energy will be used. The global demand for electrical energy is constantly growing. While there is no shortage of fossil fuels, environmental concerns are a strong driver for the uptake of renewable sources. Among a variety of renewable energy sources, PV is one of the major sources of distributed renewable energy [1] and is predicted to become the biggest contributor to electricity generation among all renewable energy candidates by 2040 [2]. It is also environmentally friendly and produces electricity with no harmful emissions. The use of distributed PV is growing across the world as an alternative. Energy storage is sometimes integrated to improve availability. Residential customers are showing great interest in integration of distributed PV generation in the form of roof-top domestic systems. The total solar power installations in the world exceeded 177GW at the end of 2014 [3]. A large part of this total PV is installed as single phase rooftop PV by the customers at their premises in LV distribution networks. Over 30 countries are currently participating in PV installation, and 20 countries had already passed their 1GW mark at the end of 2014. The International Energy Agency (IEA) has estimated that the world's PV capacity will increase up to 308GW by 2018. In Australia, PV installations are mostly residential in the form of rooftop solar PV, but there are also a growing number of commercial rooftop systems. The growth in solar PV installations is significant and still

continues strongly as new generations of households are looking forward to solar to limit the rising cost of existing grid-based electricity. Rooftop solar PV installations in Australia reached a capacity of more than 4.5 GW in 2015 as reported in [4].

### 1.2. Integration of distributed PV generation in LV distribution network

The adoption of PV energy globally is growing and part of this PV generation is being integrated into LV distribution networks. The existing distribution networks were primarily constructed without considering the possibility of large scale PV penetration into the LV distribution networks. Most of the existing distribution networks are of the radial type where the power flows from upstream transformers on the medium voltage networks to downstream LV networks. The usual behaviour of LV distribution networks may change depending upon the level of PV penetration. For example, the voltage profile of any distribution network is directly impacted by the level of PV penetration on it. Due to the increased level of PV penetration into LV distribution networks, the loads generally consume a significant portion of power locally from the installed PV while consuming reduced power from the distribution networks. This causes significant voltage variation in the LV distribution networks which is not desirable and should be managed so as to remain within acceptable limits. In some cases, the direction of power flow may become reversed in parts of the distribution network when the solar generation by the PV modules exceeds the feeder load demand [5]. Change of network voltage profile and reversal of power flow direction are the most significant power quality issues that may appear in LV distribution networks with the inclusion of distributed generation [6]. In addition, unbalanced variation in voltage may also occur due to the unbalanced solar generation or unbalanced loading in four-wire LV distribution networks. This may cause an undesirable low voltage on one phase while increasing the voltage of remaining phases, which is potentially damaging for electric appliances [7]. In addition, over-voltage is a common phenomenon observed in LV distribution networks with high penetration of residential roof-top PV. For instance, during the middle of any day of a working week, the solar generation may be higher than the load demand. In such cases, high voltages may cause inverter tripping and the subsequent loss of solar generation. In addition, high PV penetrations also causes several other power quality problems including voltage unbalance, voltage drop/rise and voltage flicker etc. which limit the capability of distribution networks to allow a large quantity of PV penetration. All these impacts may limit the level of PV penetration within the LV distribution networks.

# 1.3. Compensator for LV distribution networks with distributed PV generation: A Unified Power Flow Controller (UPFC) Proposal

To achieve higher penetration of renewable generation within the LV distribution networks while preventing loss of solar generation, the incorporation of intelligent control, storage or regulatory devices are required in the LV distribution networks [8, 9]. The authors of [8] propose a coordinated control of distributed energy storage with tap changing transformers for voltage rise mitigation. Integration of batteries as storage devices with PV systems are proposed in [9] which shows that storage can shift the peak demand by allowing the PV/storage system to charge during high solar generation periods on off-peak and discharge during peak load conditions. An energy storage system (ESS) is proposed as an intelligent active-management solution for mitigating voltage unbalance with high PV penetrations in LV distribution networks [10]. The authors showed that an ESS is capable of reducing the voltage unbalance factor as well as power losses in the networks. Some other methods for improving voltage unbalance are proposed and discussed in [11] where the authors firstly proposed increasing the cross-sectional area of feeders to reduce the voltage drop along the feeder. Since the distribution networks have already been constructed and are in service, it will not be economical to reconstruct the networks by

increasing feeder cross-section. Significant improvement in voltage unbalance can be achieved by the installation of capacitor banks in LV distribution feeders. It is shown that, with the help of proper operational commands for capacitor regulator, the voltage unbalance can be effectively improved by shifting the voltage profiles to within an acceptable range. Finally, the authors proposed to combine two techniques for improving voltage unbalance and found a significant improvement by this method compared applying those techniques separately. Two fundamental methods, namely on-load tap-changing (OLTC) and capacitor installation (either fixed or switched) are discussed for voltage regulation in LV distribution networks under high PV penetrations [12]. OLTCs are typically constructed as autotransformers with automatically adjusting taps and used to increase the voltage along the feeder under load. The permissible voltage increase provided by the OLTC for voltage regulation along the feeders is limited by the presence of loads (customers) near the OLTC. If there is a load near the OLTC, then first house protection is required to protect this customer from overvoltage [12]. On the other hand, due to the continuously varying nature of loads and PV penetration, fixed capacitors are not suitable for supplying the reactive power demanded by the load. OLTCs and switched capacitors are not suitable for voltage regulation along the feeder for such varying loads and variable PV penetration because they may not respond quickly enough to voltage variation. The possibility of inverters to support the necessary reactive power for voltage regulation is described in [12]. However, the IEEE 1547 standard, which is a guideline for interconnecting distributed resources with electric power systems, does not currently permit the PV inverter to actively regulate the voltage at the point of common coupling (PCC) [13]. Moreover, [12] also mentioned that the UL 1741 standard does not allow the inverter's participation in voltage regulation. The Australian PV Association has recently published a report [14] indicating that the AS4777 standard for grid connection of energy

systems via inverters recommends that inverters be set to operate at unity power factor. Due to the limitations imposed by AS4777, IEEE 1547 and UL 1741, PV systems are only designed to operate at unity power factor at present. At this point, researchers should look for intelligent controls for meeting the challenges of voltage regulation, voltage unbalance, overvoltage and phase balancing which occurs in LV distribution networks due to high PV penetrations.

Flexible AC Transmission System (FACTS) devices employing solid state electronics can respond almost instantaneously to manage voltage variation within the LV distribution networks. Specific FACTS devices include the Static Compensator (STATCOM), Dynamic Voltage Restorer (DVR) and UPFC. Recent research in LV distribution networks with PV are mainly focused on voltage regulation, voltage balancing, line loss minimisation, voltage profile correction and active filtering. The use of FACTS devices to mitigate those problems is being extensively studied. For example, the effectiveness of Distribution Static Compensator (DSTATCOM) and DVR devices are investigated for voltage unbalance reduction and voltage profile correction within LV distribution networks with high PV penetrations [15]. A UPFC is used as a centralised control device for simultaneously controlling all node voltages and line losses in a loop distribution system to ensure better service quality [16] where an electrolytic capacitor of about 3000 μF is used as a DC bus. These electrolytic capacitors are quite costly, large in size and often determine the working temperature of the converters. In addition, the failure rate of such capacitors is significant [17, 18].

Current research with UPFC is focused on the reduction of DC bus capacitance value to optimize its size, cost and lifetime. A UPFC with a three-leg parallel converter and a four-leg series converter, (3+4 leg UPFC) is proposed for LV distribution networks in [19]; this

work was based on simulations only conducted in Matlab Simulink which covered the following:

- A 3+4 leg UPFC was developed with a three-leg series converter and four-leg shunt converter which shared a common DC bus. This DC capacitor was proposed to be polypropylene or ceramic.

- Control strategies for voltage regulation and DC bus voltage control were developed.

- A degree of negative sequence current compensation was provided to remove  $2\omega$  oscillations from the DC bus.

This thesis is a systematic exploration and expansion of capabilities of an extended UPFC based compensator. A UPFC based on a four-leg shunt converter and a four-leg series converter, (4+4 leg UPFC), with reduced DC bus capacitance is introduced. This has a full range of series and parallel compensation duties and is a significant extension of the previous work [19]. This thesis includes results from a laboratory scale prototype for experimental verification. This thesis introduces new control features for series and parallel compensation using the UPFC based compensators. The addition of a fourth leg in the shunt converter provides an additional degree of freedom. The additional features covered in this thesis are:

- The sequence based synchronously rotating frame method is established to regulate the load voltages through a four-leg series converter and a series injection transformer.

- The zero sequence voltage compensation technique is established to remove the zero sequence voltage which appears at the output terminal during any unbalanced operation of the system.

- Active filtering capability of the UPFC shunt converter is explored to provide harmonic compensation.

- Zero sequence current compensation is established with the addition of a fourth leg in shunt converter.

- Reactive current compensation is provided which allows the power factor correction of the system.

- DC bus voltage control strategies are extended to cover the cases when the shunt converter is able to provide zero sequence, reactive current and harmonic current compensation.

- The instantaneous power flow analysis of UPFC are derived and presented for the 4+4 leg case.

- An equation is provided to calculate the DC bus capacitor size if the shunt converter is controlled to provide harmonic current compensation.

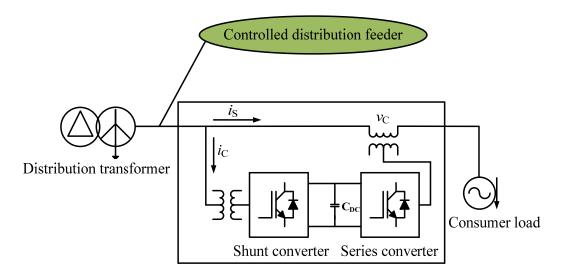

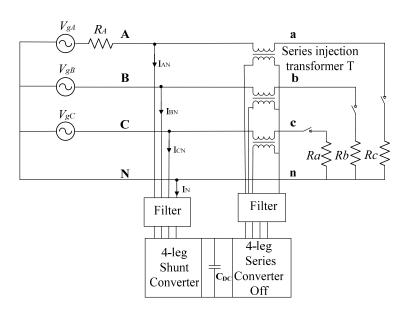

As the electrolytic capacitor of several thousands of microfarads is now replaced by a ceramic capacitor of tens of microfarads, the major research challenge is to control the 4+4 leg compensator and the DC capacitor voltage by ensuring instantaneous power balance for the input and output converters [20]. Figure 1.1 represents the basic schematic of a typical UPFC as presented in [21] redrawn with some modifications. It consists of a combination of two switching converters, i.e., series and shunt converters and the DC terminals of which are connected to a common DC bus capacitor. This UPFC arrangement can function as an AC to AC power converter where real power can freely flow in either direction between the AC terminals of the two inverters. Moreover, each inverter can independently generate or absorb reactive power at its own AC output terminal. The series converter performs voltage compensation duties by injecting AC voltage ( $v_C$ ) with controllable magnitude and phase angle in series with the distribution feeders by means of a series transformer. The shunt converter provides the current compensation through the common

DC link to meet the power requirement by the series converter. It also regulates the DC bus voltage.

Figure 1.1 Schematic of unified power flow controller (UPFC) [21]

### 1.4. Aims and objectives of the research

The research program has the following central challenges:

- To develop control models based on averaged representations of the UPFC converters.

- To extend the instantaneous power balance analysis of UPFC with a view to controlling the DC bus voltages for the cases where the DC bus capacitors are small.

- To simulate suitable control models for the converters in the Matlab Simulink environment.

- To confirm the capability of a 4+4 leg UPFC based compensator to simultaneously provide voltage and current compensation for LV distribution networks with high PV penetrations by simulation.

- To build a laboratory scale 4+4 leg UPFC based compensator prototype for experimental works using commercial inverter module (STGIPL14K60).

- To develop the control software for the experimental tests of the 4+4 leg UPFC based compensator.

- To perform the experimental verification of the UPFC and its control algorithms on a laboratory scale prototype.

### 1.5. Organisation of the thesis

This thesis is organised into seven chapters. Chapter 1 covers the general background, objectives and motivation of the research work. The potential contribution of this research is also discussed in this chapter. Chapter 2 discusses the literature review which included the recent PV scenarios globally and in Australia, the benefits and impacts of high PV penetration in LV distribution networks and mitigation techniques. The research gap is also discussed in this chapter. In Chapter 3, modelling and control strategies of the proposed 4+4 leg UPFC are developed in the continuous time domain. The instantaneous power flow equation is also developed for three cases i.e., voltage regulation, active filtering and ancillary services. The simulation results are presented in **Chapter 4** and are divided into two sections. Section 4.3 discusses the results when the UPFC based compensator is applied in the LV distribution feeder for voltage regulation with only zero sequence current compensator. The simulation results are also shown when the UPFC is configured for voltage regulation with both zero sequence and reactive current compensator. Section 4.4 discusses the simulation results when the UPFC based compensator is applied in LV distribution networks for active filtering. Chapter 5 describes the hardware design and construction for the project, the experimental system architecture and the filter design considerations for damping, the phase locked loop arrangement and the algorithm used for the 4+4 leg converter for modulation. The current, voltage and the DC bus voltage regulation system architecture and their control systems are presented. The experimental results are also presented and discussed in this chapter. An overview discussion, conclusions and the directions of future work are presented in **Chapter 6**. Appendix A which records the details of the development boards including the experimental circuit board, schematic diagrams and the PCB layout of the development board is presented in **Chapter 7**.

### 1.6. Conclusion

This chapter covers the general background of distributed renewable energy systems and the potential contribution of PV energy in power generation. This chapter also discusses the challenges and probable implications for integration of high PV generation within LV distribution networks. A brief discussion is carried out into the merits and demerits of the possible solutions available for voltage management with distributed PV generation. A UPFC is proposed as a compensation device for mitigating potential complications faced by LV distribution systems having to cope with high PV integration. The major aims and objectives of the research are also presented in this chapter.

### **Chapter 2 LITERATURE REVIEW**

### 2.1. Introduction

The installed capacity of PV systems globally reached 177GW at the end of 2014. The annual rate of installations, 38.7GW in 2014, continues to increase. A large part of this is installed as residential systems connected to LV networks. The majority of the LV distribution networks are radial, unbalanced with respect to loads and feeder structures and have high feeder line resistance to reactance R/X ratios. The large scale deployment of PV within the LV distribution networks is limited by voltage quality problems, particularly over voltages and unbalance. Development of proper mitigation techniques is essential to effectively and efficiently manage high penetration of PV within the LV distribution networks. A number of techniques have already been developed and implemented in LV distribution networks to alleviate those problems. This chapter provides an extensive review of the present status, impacts and technical challenges of PV penetration in LV distribution networks. In addition, the review comprehensively examines the commercially available and emerging mitigation methods and provides a framework that systematically explores the full range of technical methods and limitations for PV impact mitigation.

### 2.2. Recent historical advancement of cumulative PV installation

### 2.2.1. Global PV scenario

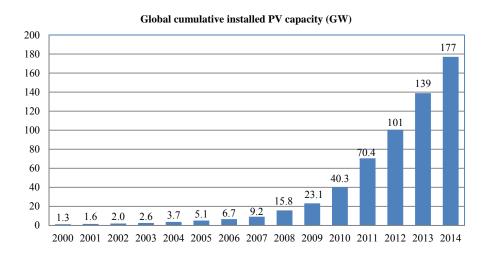

The global PV market has grown rapidly over the past decade at a steadily increasing rate which will lead to PV becoming one of the major sources of power generation for the entire world [22]. The global PV market had a record year in 2014, installing more capacity than any other renewables after hydropower while exceeding wind power [23]. Figure 2.1 shows the progress of cumulative installed PV capacity in the world over the period 2000-2014. A major portion of the total PV capacity is integrated with LV distribution networks in the form of rooftop domestic systems. According to the European

Photovoltaic Industry Association (EPIA) report, rooftop PV installations were more than 23GW in 2013 which exceeded the utility scale installations significantly [22].

Figure 2.1 Progress of total global cumulative installed PV capacity (2000-2014) [3, 22]

Table 2.1 presents numerical data for actual cumulative PV installed capacity by region with global market share in 2013, and forecasts of those numbers for 2018. Europe is the world's leading region in terms of cumulative installed capacity with 81.5GW as of 2013 that represent about 59% of the world's cumulative PV capacity. However, the global market share of PV capacity in Europe is slightly down in 2013 from 70% in 2012 and about 75% of the world's capacity in 2011. Asia Pacific countries are also still growing fast, having about 21.9GW of cumulative PV installed capacity representing 16% of the world's capacity in 2013. China is in the top rank within the Asia Pacific countries, recording 18.6GW of cumulative installed capacity with 13% of market share in 2013. The Americas is improving its position compared to other countries in respect of cumulative installed capacity. The Americas achieved 13.7GW cumulative installed PV in 2013 which was a global market share of 10%. Several countries from large Sunbelt regions like Africa, the Middle East, South East Asia and Latin America are on the brink of starting their development. For example, the cumulative installed capacity outside Europe was 30GW in

2012, but doubled during 2013 to reach 60GW. This indicates the ongoing rebalancing between Europe and the rest of the world and closely reflects changing patterns in electricity consumption [22]. The share of PV installations outside Europe can only increase, ensuring the ongoing development of the PV market globally.

Table 2.1 Global PV cumulative installed capacity and market share per region in 2013 and forward forecasts

| _               | 2013                    |                        | 2014                    |                        | 2018                    |                        |

|-----------------|-------------------------|------------------------|-------------------------|------------------------|-------------------------|------------------------|

| Region          | Installed capacity (GW) | Market<br>share<br>(%) | Installed capacity (GW) | Market<br>share<br>(%) | Installed capacity (GW) | Market<br>share<br>(%) |

| Americas        | 13.7                    | 10                     | 22                      | 11                     | 64.5                    | 15                     |

| Asia Pacific    | 21.9                    | 16                     | 34                      | 18                     | 82                      | 19                     |

| China           | 18.6                    | 13                     | 34                      | 18                     | 103                     | 24                     |

| Middle East and | 0.9                     | 0.6                    | 3.8                     | 2                      | 21.5                    | 5                      |

| Africa          |                         |                        |                         |                        |                         |                        |

| Rest of World   | 2.0                     | 1.4                    | 1.90                    | 1                      | 4.3                     | 1                      |

| Europe          | 81.4                    | 59                     | 95.3                    | 50                     | 155                     | 36                     |

| Total           | 138.5                   | 100                    | 191                     | 100                    | 430.3                   | 100                    |

The data for 2014 and 2018 is based on EPIA's "high scenario" [22]

The combination of declining European markets and the possibility of establishing durable new markets in developing countries could cause this market to boom. As a result, the Asia-Pacific region, including China, should represent a major share of PV installations in the coming years under the EPIA's high scenario [22]. There is a possibility of reaching up to 430.3GW of PV systems within five years from 2013 for the best cases as compared to 138.9GW at the end of 2013.

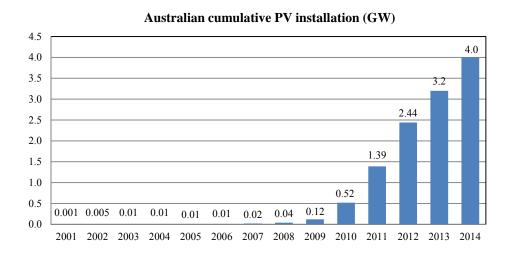

### 2.2.2. Australian PV scenario

The Australian Renewable Energy Target (RET) has been established with the mandate of generating 20% or 45TWh of Australia's electricity supply from renewable energy sources by 2020 while reducing greenhouse gas emissions [24, 25]. A wide range of initiatives have been taken by several state governments to promote the installation of small scale PV in Australia. Feed-in tariffs (FIT) existed in the early stages of the development of the residential PV market. The RET currently provides installation rebates and encourages

investment in small scale installations, especially for solar PV and hot water systems in households [25]. The continuous rise in grid electricity prices and the various incentives provided by the state governments make PV a cost effective option for homeowners, as well as of increasing interest to the commercial sector across Australia [26]. Module prices continued to drop from 1.3 AUD/W in 2012 to around 0.75 AUD/W in 2013, and installed prices for small residential systems dropped from an average of around 3 AUD/W to around 2.50 AUD/W [26]. Over 1 million Australian homes now have a PV system, and residential penetration levels average 15% and are over 30% in some areas. The Australian Photovoltaic Institute (APVI) has recently reported that the small scale cumulative PV installed capacity has reached more than 4.5 GW in 2015 [4, 27] as shown in Figure 2.2. The growth in solar PV in Australia is quite significant. The cumulative installed capacity was about 1.39 GW in 2011 and reached 2.44 GW during 2012. However, the Australian PV market has contracted in 2013, with installation levels reducing from more than 1 GW installed in 2012 to around 850 MW [26].

Figure 2.2 Progress of cumulative small scale installed PV capacity in Australia since April 2001 [4, 27]

The probable reason is the withdrawal of FITs by most State Governments. Electricity network operators also impose restrictions on further installations to cope with potential

issues arising from high penetration levels. According to a report of the APVI supported by the Australian Renewable Energy Agency (ARENA), PV system sizes have still continued to increase despite these restrictions on PV power exports to the grid and low or zero rates now paid for exported power [27].

### 2.3. Benefits of high Solar PV penetrations